Le fait qu'Intel et AMD s'associent pour fournir un produit concurrent est un signe clair de la domination de Nvidia sur le secteur des accélérateurs. La semaine dernière, AMD et Intel, mais aussi Broadcom, Cisco, Google, Hewlett Packard Enterprise, Meta et Microsoft, ont créé l’Ultra Accelerator Link (UALink) Promoter Group pour développer des interconnexions à grande vitesse entre les processeurs et les accélérateurs. Nvidia dispose déjà de la technologie NVLink, qui permet à ses processeurs de communiquer entre eux et de partager des données à une vitesse extrêmement élevée. Avec la technologie d'interconnexion d'accélérateurs à grande vitesse UALink, les concurrents de Nvidia s'associent pour faire la même chose avec leurs propres puces. Le partenariat entre Microsoft, Meta et Google peut sembler improbable, mais tous fabriquent des processeurs personnalisés pour leurs services cloud. « La première étape pour UALink est de définir et d'établir une norme industrielle ouverte pour que les accélérateurs d'IA puissent communiquer plus efficacement », a expliqué le groupe. Selon les partisans d'UALink, une interconnexion basée sur des normes ouvertes devrait permettre aux équipementiers, aux professionnels de l’IT et aux intégrateurs de systèmes de faciliter l’intégration, d’améliorer la flexibilité et l’évolutivité de leurs centres de données connectés à l'IA.

L'IA et le calcul haute performance (HPC) nécessitent de déplacer une quantité considérable de données entre les cœurs et la mémoire. Afin de construire ses interconnexions à haut débit NVLink, Nvidia a exploité la technologie de réseau à haut débit acquise en 2019 avec le rachat de Mellanox pour 6,9 milliards de dollars. « Quand on regarde les besoins des systèmes d'IA dans les centres de données, il apparaît très clairement que les modèles d'IA continuent de croître massivement », a déclaré Forrest Norrod, vice-président exécutif et directeur général du groupe des solutions pour centres de données chez AMD, lors d'une conférence téléphonique avec les médias. « Cela signifie que pour les modèles les plus avancés, de nombreux accélérateurs doivent travailler de concert pour l'inférence ou l'entraînement. La possibilité de faire évoluer ces accélérateurs sera d'une importance capitale pour améliorer l'efficacité, les performances et l'économie des systèmes à grande échelle à l'avenir ».

Unifier les fournisseurs pour contre Nvidia

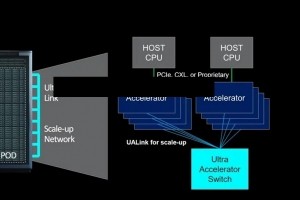

Le groupe UALink prévoit de développer une spécification pour définir une interconnexion à grande vitesse et à faible latence pour les communications à grande échelle entre les accélérateurs et les commutateurs dans les modules de calcul de l'intelligence artificielle. Selon le groupe, avec la spécification 1.0, il sera possible de connecter jusqu'à 1 024 accélérateurs au sein d'un pod de calcul IA et d’effectuer des opérations de chargement et de stockage directement au niveau de la mémoire attachée aux accélérateurs, tels que les GPU, dans le pod. M. Norrod a fait remarquer que les membres d'UALink soutiennent également l'Ultra Ethernet Consortium (UEC), créé pour développer des technologies visant à augmenter l'échelle, la stabilité et la fiabilité des réseaux Ethernet afin de répondre aux exigences de l'IA en matière de réseaux à haute performance. Fondé l'année dernière par AMD, Arista, Broadcom, Cisco, Eviden, HPE, Intel, Meta et Microsoft, l’UEC compte aujourd'hui plus de 50 fournisseurs. Dans le courant de l'année, le consortium prévoit de publier des spécifications officielles qui se concentreront sur une série d'améliorations dans la mise à l’échelle de l'Ethernet, notamment de meilleures options de livraison de paquets et de trajets multiples, ainsi que des fonctions modernes de congestion et de télémétrie. « Cette interconnexion au niveau du pod promue par le groupe UALink peut répondre à un aspect important des futures architectures de systèmes d'intelligence artificielle à grande échelle. Et de concert avec Ultra Ethernet, il permettra à des systèmes de centaines de milliers ou de millions d'accélérateurs de travailler efficacement ensemble », a estimé M. Norrod.

Dans une déclaration annonçant la formation du groupe, J. Metz, président de l'Ultra Ethernet Consortium, a vanté les possibilités de collaboration entre UALink et les partisans de l'UEC : « En très peu de temps, l'industrie technologique a relevé les défis introduits par l'IA et le HPC. L'interconnexion d'accélérateurs comme les GPU nécessite une perspective holistique si l’on veut améliorer l'efficacité et la performance. À l’UEC, nous pensons que l'approche scale-up d'UALink pour résoudre les problèmes des clusters de pods complète notre propre protocole scale-out, et nous sommes impatients de collaborer à la création d'une solution ouverte, respectueuse de l'écosystème, à l'échelle de l'industrie, qui répondra à ces deux types de besoins à l'avenir ». L’UALink Promoter Group prévoit de livrer la spécification 1.0 au troisième trimestre de cette année. Elle sera mise à la disposition des entreprises qui rejoignent l’Ultra Accelerator Link (UALink) Consortium. Des produits pourraient apparaître l'année prochaine, avec une implémentation possible autour de 2026.