Attendue depuis près de deux ans, la refonte de la famille Intel Xeon vient enfin de démarrer. Exit les Xeon Scalable, le fondeur semble simplifier ses dénominations avec l’introduction des Xeon 6 Serie-P (Granite Rapids) et surtout Serie-E (Sierra Forest). Pour la première fois depuis près d’une décennie (personne ne regrette vraiment les Xeon E3 et les Atom S1200 et C2000), Intel propose deux architectures serveur différentes les P-cores performance (reposant sur des coeurs Redwood Cove) et les E-cores efficiency (avec des coeurs Crestmont, déjà utilisés sur les Core Ultra Meteor Lake) : bien que les deux plateformes partagent des technologies de base, les instructions AVX-512, AMX (très utiles pour l’accélération IA) et l’hyperthreading ne sont pas présents sur les E-cores (voir slide ci-dessous). Pour la fabrication, Intel utilise un procédé Intel3 pour les tuiles compute (les coeurs) et Intel 7 pour les tuiles I/O de ses puces Xeon 6 (P et E).

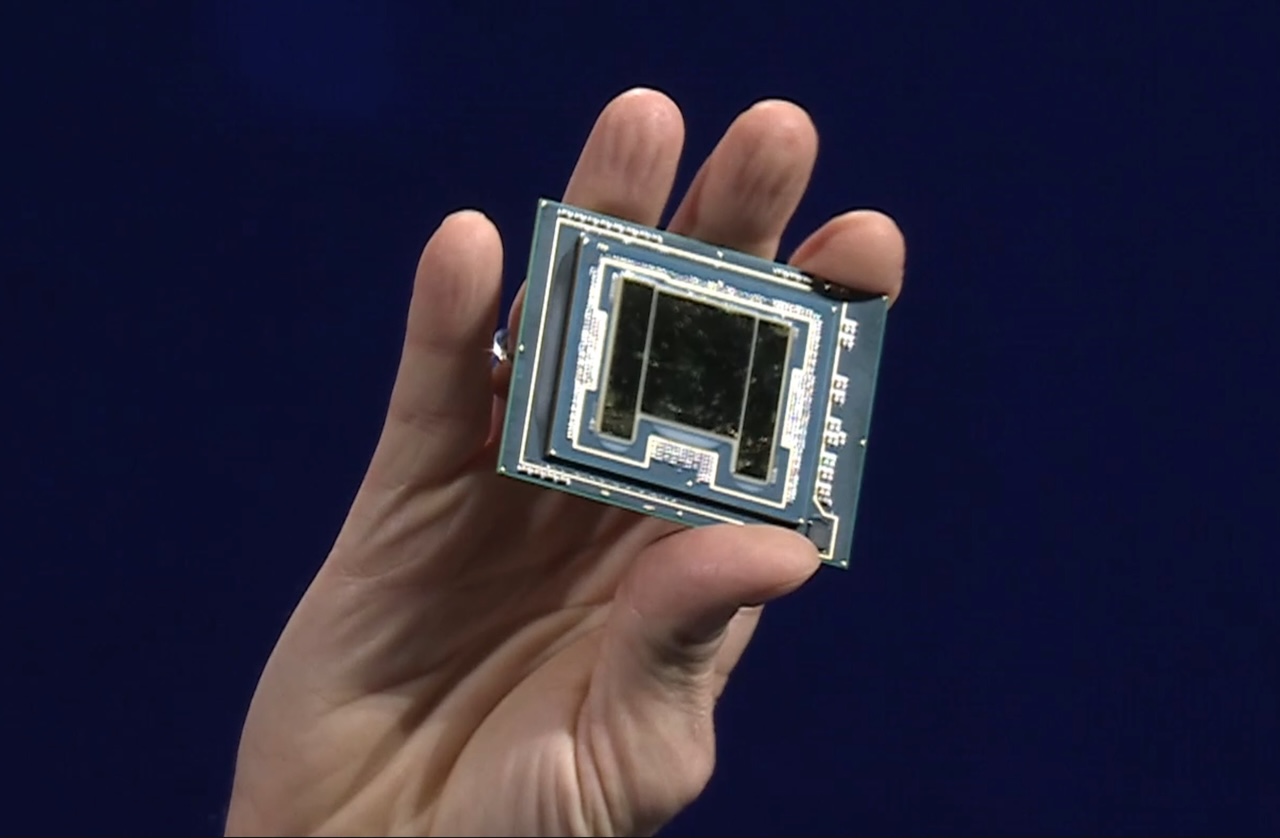

Avec les Xeon 6, Intel utilise la gravure Intel3 pour les coeurs et Inte7 pour le SoC. (Crédit Intel)

Les puces P-cores ont été conçues pour offrir des performances maximales par thread (HPC, IA, virtualisation et logiciels licenciés au coeur chez Microsoft et VMware) et les processeurs E-cores taillés pour les charges de travail où la recherche de l'efficacité énergétique est supérieure à celle de la simple performance afin de pour réduire les coûts de fonctionnement. Dans les instances cloud notamment, où les vCPU sont plébiscités par les hyperscalers pour multiplier les instances à moindre coût. La famille E-cores - avec le Xeon 6 6766E (144 cœurs Crestmont sans hyperthreading avec 12 slots DDR5 et 96 lignes PCIe Gen5 dans une enveloppe TDP de 250W) - était très attendue afin de rivaliser avec les serveurs Arm, qui se multiplient chez les hyperscalers (Ampere, AWS Graviton, Azure Cobalt, GCP Axion et surtout Nvidia Grace). Le 6766E semble tailler pour concurrencer l’Ampere Altra Max (de 80 à 128 coeurs Arm), encore limité à la DDR4 et au PCIe 4.0, et sans support du CXL. L’idée est de maitriser la consommation électrique des cœurs x86, afin de limiter la fuite des charges de travail vers les plateformes Arm, qui nécessitent un portage applicatif pour cause de changement d'architecture. Avec les Xeon 6 E-serie, Intel propose à ses clients d'abandonner leurs vieux serveurs x86 (Xeon Scalable de 1e/2e génération) pour bénéficier d'une plateforme plus moderne sans recompiler leurs applications nécessitant des performances modestes.

Intel scinde le marche des serveurs en deux avec d'un coté les puces pour l'IA, le HPC et les logiciels facturés au coeur, et de l'autre les instances plus légères. (Crédit Intel).

En entrée de gamme, le Xeon 6 6710E démarre avec 64, 96, 112 ou 128 cœurs Crestmont fonctionnant à 2,4 GHz (3,2 GHz en mode turbo sur tous les cœurs). En haut de gamme, on trouve le 6766E avec ses 144 cœurs E et un TDP de 250 W, qui fonctionne à une fréquence de base de 1,9 GHz (2,7 GHz en turbo pour l'ensemble des cœurs). Ensuite, il y a le 6780E, également avec 144 cœurs, mais avec un TDP plus élevé de 330W, ce qui lui permet d'avoir une fréquence de base de 2,2GHz (3 GHz en turbo sur tous les coeurs). Ces deux derniers processeurs disposent de 108 Mo de cache L3, et le petit 6710E dispose de 96 Mo. Tous les processeurs Xeon 6 E-core disposent également de 96 lignes PCIe 5.0 et 64 voies CXL 2.0. En mode composable, le CXL permet de créer des pools de ressources mémoire, comme un système Numa, flash, GPU ou Ethernet via l’interface PCI. Précisons qu’au premier trimestre 2025, Intel introduira des big sockets (LGA7529) avec le 6900E Sierra Forest-AP avec 288 cœurs et une enveloppe thermique de 500W, disponible en mono et double socket. Les 6700E reposent sur le socket LGA4710 (small socket).

La base technique est proche, mais les Xeon 6 E font l'impasse sur les instructions AVX-512, AMX et l'hypertheading. (Crédit Intel)

Avec sa haute densité reposant sur des E-Core, le Xeon 6 6700E permet un gain de performance allant jusqu'à 4,2x et une réduction par watt allant jusqu'à 2,6x pour le transcodage vidéo par rapport au Xeon Scalable de 2e génération a expliqué Pat Gelsinger, le CEO d’Intel lors de sa présentation à Computex 2024. Et la consolidation au niveau du rack atteint les 3 pour 1, ce qui réduit considérablement l’encombrement des baies dans un datacenter et permet donc d’augmenter le nombre de serveurs. Ces dernières années, Intel a travaillé à l’amélioration de la performance par cœur sur ses E-cores. Ces derniers ne sont plus seulement des coeurs moins rapides, ils se hissent au niveau des performances d'un cœur Xeon E5 V4 ou d'un Xeon Scalable Emerald Rapids, a expliqué le fondeur.

Les puces Xeon 6 6700E seront disponible au 3e trimestre 2024. (Crédit Intel)

Les processeurs Intel Xeon 6 avec des P-cores devraient être lancés au premier trimestre 2025 et offriront de meilleures performances pour les charges de travail les plus exigeantes, notamment l'IA, le calcul haute performance, le traitement d'images et l'analyse de données. En haut de gamme, Intel positionne le 6900P (big socket LGA7529) avec jusqu’à 128 cœurs (Redwood Cove), 12 canaux de mémoire et la possibilité d'utiliser des modules DIMM MCR, qui apportent une bande passante proche de celles des Xeon Max, mais sans nécessiter le recours à la mémoire HBM, très onéreuse et de plus faible capacité. Cette puce supporte 96 lignes PCI 5.0 (jusqu'à 136 en version mono socket) et 64 voies CXL 2.0. En entrée de gamme, on retrouve les 6700P (single socket LGA4710) avec 16, 48 ou 86 coeurs P (Redwood Cove) et les mêmes I/O (voir slide). On s’y perd un peu avec toutes ces références P-serie et E-serie sur des sockets différents et disponibles à des dates éloignées : 6700E au 3e trimestre 2024 et 6900P, 6900E et 6700P au premier trimestre 2025.

Avec ses deux séries de puces, Intel trace la voie de sa futur gamme serveurs, qui seront plus spécialisés tout en conservant une architecture totalement compatible sur un même écosystème logiciel. La menace aujourd’hui ne provient plus vraiment d’AMD, mais bien des systèmes reposant sur l’architecture ARM, qui séduit un grand nombre d’hyperscalers.