A l’occasion de son Architecture Day 2020, Intel a livré plus de détails sur la prochaine puce Tiger Lake, notamment son architecture CPU Willow Cove et son GPU Xe intégré. Le fondeur a également promis une augmentation spectaculaire des fréquences d’horloge de la puce par rapport aux puces des générations actuelles. L’entreprise affirme que, grâce à une mise à jour du transistor, le CPU de Tiger Lake offrira un saut de performance supérieur à celui de la génération précédente. Mais on n’en saura pas plus à ce sujet pour l’instant. Par contre, comme il l’avait fait en amont de la sortie de la génération Ice Lake actuelle, le fondeur a dévoilé quelques caractéristiques de base de la future plateforme, dont le PCI Express Gen 4 et le Thunderbolt 4.

La puce Tiger Lake d'Intel n'est pas une surprise. L’an dernier, le fondeur avait communiqué sur ses projets et ajouté le CPU à sa feuille de route publique. À l'époque, Intel avait annoncé que Tiger Lake serait basée sur une autre architecture, qu’elle offrirait la première intégration avec son cœur Xe, la récente technologie d'affichage et la technologie I/O de dernière génération.

Le fondeur a également promis « un grand évènement » pour le 2 septembre, comprendre le lancement de Tiger Lake, comme le mentionne son site de relations avec les investisseurs, une information confirmée par les représentants d'Intel. L'une des rares choses que l’on sait avec certitude, c’est que plus de 50 ordinateurs portables Tiger Lake seront livrés d'ici les fêtes de fin d’année. Et pour éviter les pénuries, Intel stocke plus de processeurs Tiger Lake qu’il ne l'avait prévu initialement.

La plateforme SoC Tiger Lake d'Intel est basée sur l’architecture CPU Willow Cove. (Crédit : Intel)

Un transistor SuperFin qui change la donne

En général, deux choses permettent d’améliorer radicalement les performances des processeurs : les progrès dans la technologie de fabrication et une meilleure conception globale. Ces dernières années, Intel s'est enlisé dans la première voie, obligeant le fondeur à apporter des améliorations incrémentales à chacun de ses processeurs 14 nm - Skylake, Kaby Lake, Cooper Lake, et ainsi de suite - avant de faire finalement le saut vers le 10 nm avec Ice Lake et Comet Lake.

Mais la lenteur d'Intel a permis à AMD de rendre son processeur Ryzen compétitif. Le passage à la gravure à 7 nm a sans doute permis à AMD de prendre de l'avance. Et la récente déclaration d’Intel sur les retards du passage au 7 nm a laissé craindre une nouvelle distanciation. Mais ce ne sera peut-être pas le cas.

Si les produits d'Intel tiennent leurs promesses, Tiger Lake pourrait être plus compétitif qu’on le pensait. (Crédit : Intel)

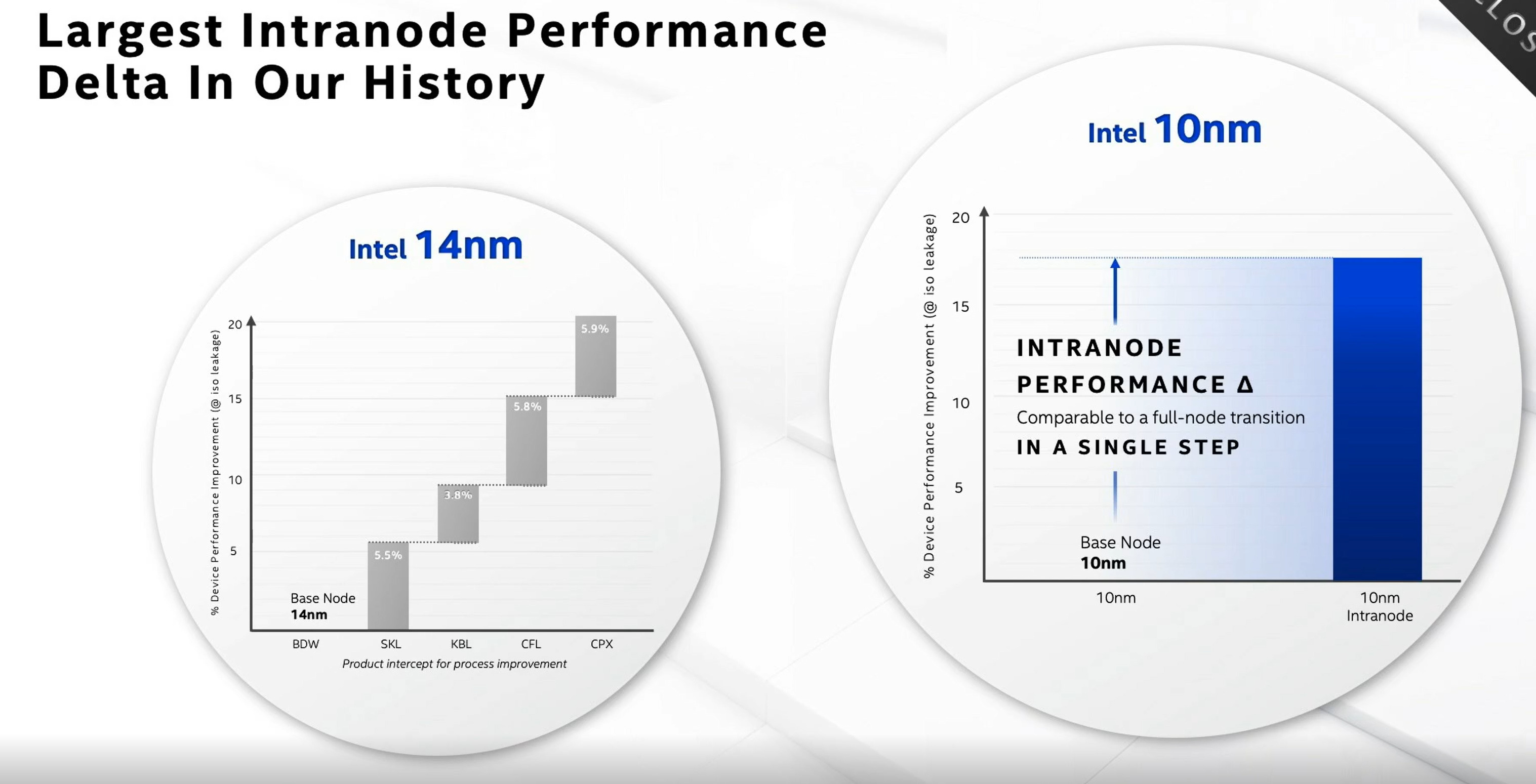

Ruth Brain, Intel Fellow spécialisée dans le développement technologique et les interconnexions, a déclaré que le gain de performance d’un intra-nœud obtenu entre Ice Lake et Tiger Lake équivalait au gain de performance de toutes les améliorations apportées aux intra-nœuds de la génération des puces à 14 nm. « C'est quasiment équivalent à une transition de gravure full-node », a déclaré Ruth Brain, laissant entendre qu'Intel était plus proche d'AMD dans le processus de fabrication qu'on ne pouvait le penser.

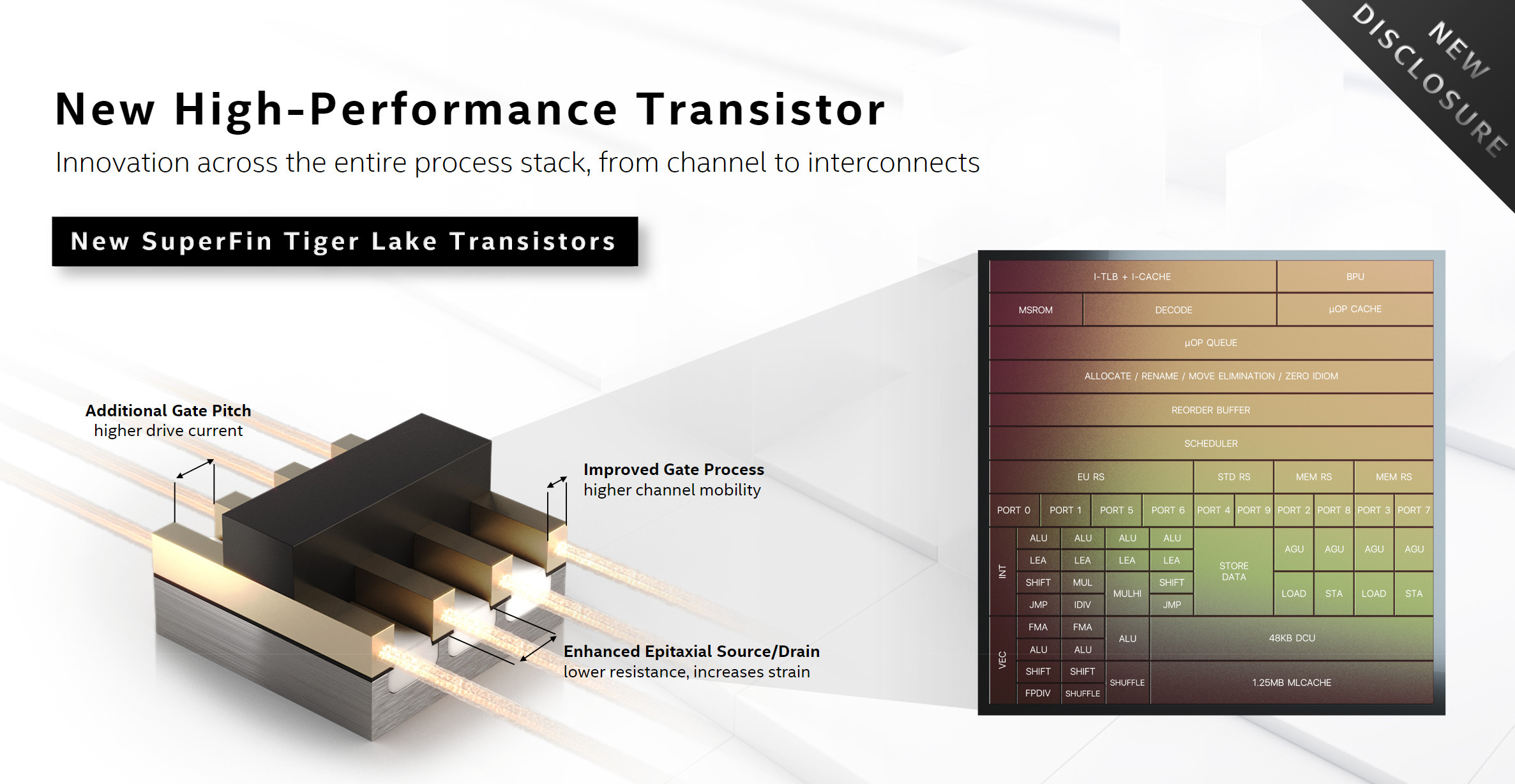

A la base des performances des puces comme Tiger Lake, on trouve un minuscule transistor. Il y a dix ans, Intel a réarchitecturé son transistor pour produire le FinFET. Aujourd'hui, le fondeur dit qu’il a créé des transistors FinFET améliorés, les « SuperFIN », avec des « condensateurs métalliques super isolants », intégrés à la pile métallique. Heureusement, ces transistors « SuperFIN » arrivent au bon moment pour compenser les problèmes de fabrication d'Intel.

Même si les consommateurs n'ont pas à se préoccuper de savoir quel transistor Intel a mis dans sa puce Tiger Lake, c’est l'un des changements fondamentaux de cette architecture et le secret de ses performances. (Crédit : Intel)

Un autre aspect plus positif concerne la nomenclature confuse « 14nm++ » qui accompagnait les discussions sur les processus de fabrication de Skylake (et que l’on pensait retrouver avec Tiger Lake). Apparemment, elle disparaît pour être remplacée par la seule désignation SuperFIN. « Il y avait tellement de « plus » que même en interne, nous avions du mal à nous y retrouver », a déclaré Raja Koduri, vice-président senior, architecte en chef et directeur général Architecture, Graphics, and Software chez Intel.

Quoi de plus pour les PC ?

Avec Tiger Lake, Intel s'est fixé un certain nombre d'objectifs, et au minimum d’offrir « davantage qu’une augmentation de performance par rapport à la génération précédente », et une « performance plus marquée dans les graphiques intégrés », et ce, sans consommer plus d'énergie que la génération des puces Ice Lake/Coffee Lake précédentes. Boyd Phelps, vice-président Client Engineering Group et directeur général du Client and Core Development Group d’Intel, a déclaré que les puces Tiger Lake seraient proposées avec un certain nombre de configurations, des dispositifs consommant moins de 10 watts jusqu’à des dispositifs consommant 65 watts

Selon M. Phelps, Intel a implémenté les transistors SuperFIN pour augmenter la performance. Le fondeur a également redessiné les circuits périphériques pour rediriger une partie de l'énergie utilisée et réaffecter l’énergie économisée pour permettre au processeur d'atteindre des cadences plus élevées sans surchauffer. Les résultats ont « largement dépassé nos attentes », a reconnu M. Phelps.

Tiger Lake est construit autour du cœur CPU Willow Cove, le même que celui des CPU Sunny Cove de Ice Lake et Comet Lake. Le cache intérieur est plus important - 1,25 Mo - pour améliorer les performances et renforcer le contrôle des flux. Cette technologie de sécurité, dont Intel a parlé au mois de juin, permet de lutter contre les attaques par saut.

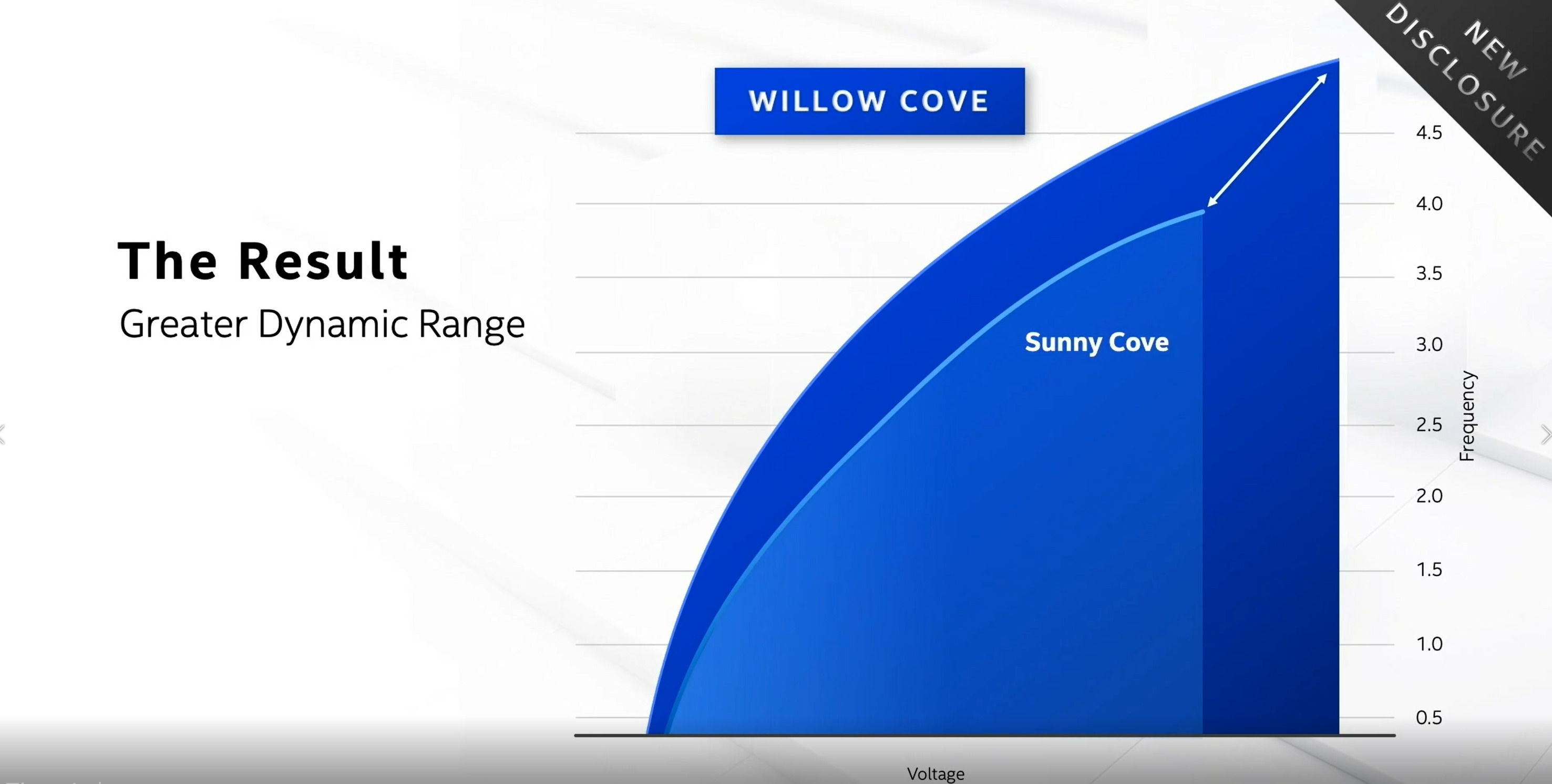

Selon Intel, Willow Cove et Tiger Lake devraient offrir des fréquences plus élevées tout en consommant moins d’énergie, le tout selon un processus à 10 nm. Notez l'axe des fréquences à droite. Est-ce une puce de 5 GHz ? (Crédit : Intel)

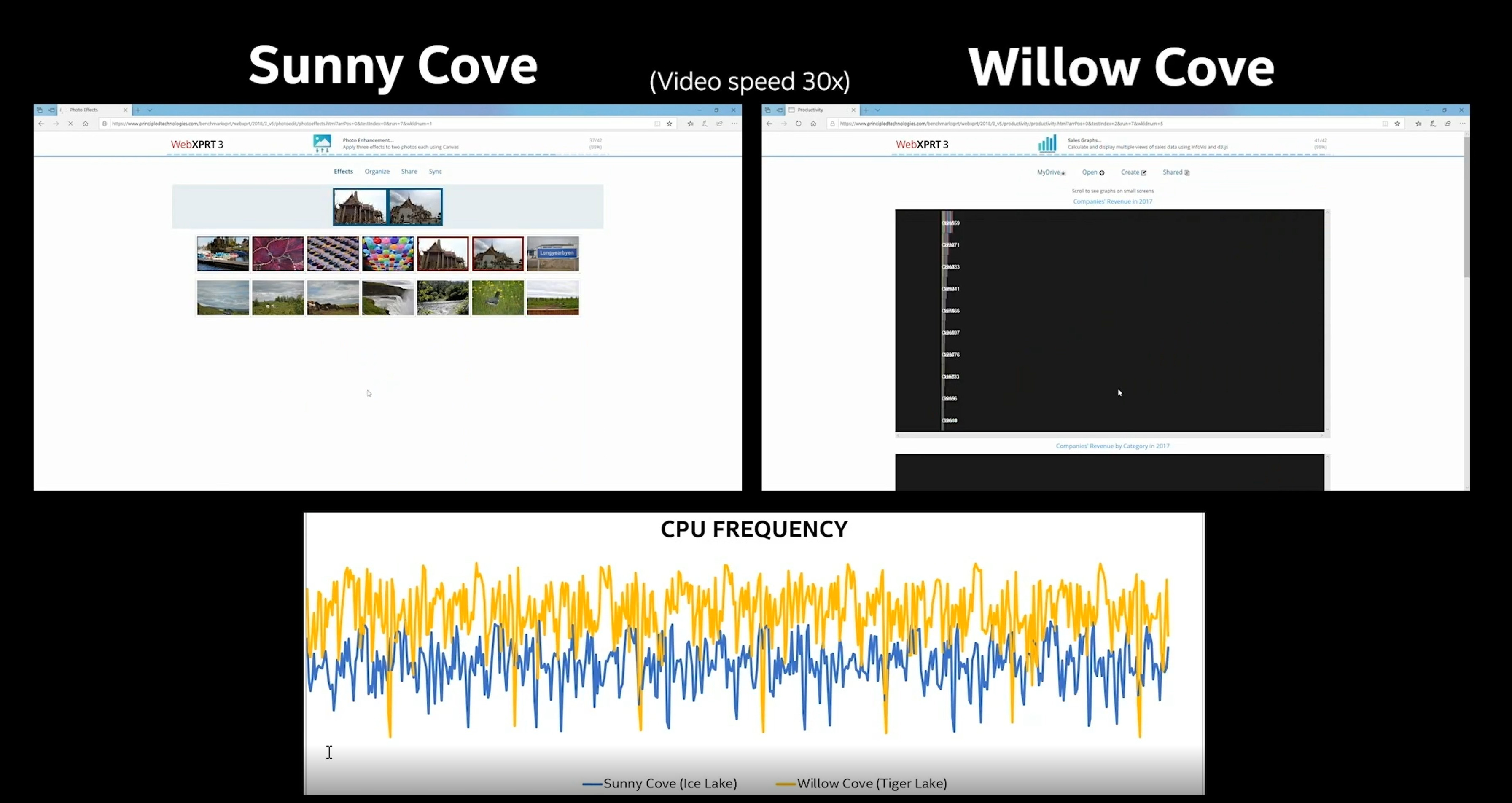

Autrement dit, la conception de Willow Cove permet une optimisation sur toute la gamme de la courbe puissance-fréquence. La puce peut être plus rapide que Sunny Cove à un niveau de puissance donné, ou elle peut fonctionner à une tension plus basse à une fréquence donnée, en consommant moins d'énergie. Dans la vidéo illustrant les différences, il semble que pour Intel, Willow Cove plafonne à une fréquence proche de 5 GHz, alors que Sunny Cove est plus proche de 4 GHz. « C'est une augmentation substantielle », a déclaré M. Phelps.

Intel a essayé de montrer que la vitesse d'horloge du CPU Willow Cove d'Ice Lake dépassait couramment celle du CPU Sunny Cove d'Ice Lake. (Crédit : Intel)

Intel a pu exploiter la même capacité de réallocation de l’énergie et de la marge thermique pour augmenter la taille du GPU intégré. C'est la première fois qu'Intel présentait son architecture Xe, annoncée il y a plusieurs années. Xe servira de base à un nouveau GPU autonome destiné aux gamers. « La version Xe LP intégrée à Tiger Lake comprend 96 UE, contre 64, qui fonctionnent à une vitesse plus rapide (mais non divulguée) que le précédent Ice Lake », a déclaré M. Phelps. Intel a également amélioré son accélérateur neural gaussien pour les activités d'intelligence artificielle, lequel permet de réduire de 20% l’usage du CPU.

Tout cela implique que Tiger Lake dans son ensemble devra être soutenu par un sous-système de mémoire plus large et plus rapide. Intel a multiplié par deux la largeur de la bande passante du fabric I/O et a inclus la prise en charge d'une mémoire plus rapide : « LP4x-4267 et DDR4-3200 DRAM pour commencer, avec à terme le support de la mémoire LP5-5400 », comme l’a déclaré M. Phelps. La fonction de chiffrement complet de la mémoire,Total Memory Encryption, a été intégrée pour protéger contre les attaques.

Une autre grande amélioration concerne le PCI Express 4.0 (ou PCie Gen4), une capacité que l’on ne trouvait que chez AMD jusqu'à présent. Ce n’est plus le cas, puisque Tiger Lake comprend un nombre - non divulgué - de voies PCIe 4.0, reliées directement au CPU, et non à un hub intermédiaire PCH I/O. (Selon Intel, cela permet d'offrir une bande passante mémoire de 8Gbits/s à des périphériques comme les SSD, ce qui implique qu’il y a quatre voies). M. Phelps a déclaré que la connexion directe PCIe 4.0/CPU réduisait de 100ns la latence de l'échange - l'idéal, selon lui, pour un GPU externe (Xe ?) par exemple. « Le nombre de voies PCIe dépendra surtout du nombre de cœurs de processeur », a-t-il précisé.

Thunderbolt 4 et USB 4 en approche

Intel se montre moins disert sur Tiger Lake qu’il ne l’avait été sur Ice Lake et il faut s’attendre à l’annonce d’autres améliorations. Contrairement à Ice Lake qui incluait des ports Thunderbolt 3, Tiger Lake sera le premier à adopter la puissante spécification Thunderbolt 4 et USB4. « Les ports USB-C connectés à un PC sous Tiger Lake seront également plus puissants », a déclaré M. Phelps. En plus du mode DisplayPort Alt Mode et de la prise en charge du tunneling, les capacités des cartes graphiques discrètes externes connectées à l'USB-C seront améliorées pour l'entrée et le multiplexage.

Intel a également révélé jeudi que Tiger Lake comporterait un chemin de données isochrone dédié à l'affichage, sur lequel l’entreprise donnera probablement plus de détails plus tard. Intel n’a toujours pas expliqué pourquoi le pipeline d'imagerie de Tiger Lake était si puissant (vidéo 4K/30, avec une feuille de route vers le 4K/90, plus le support des images fixes 27MP, avec un maximum de 42MP) sur une plateforme PC qui comprend souvent des caméras faciales de 1MP. Si l’on fait référence au modèle tick-tock abandonné par Intel en 2016, on pourrait dire que c’est le « tock » qui retentira le 2 septembre, date à laquelle Intel lancera effectivement son CPU Tiger Lake. En dévoilant les performances inattendues du GPU Xe, Intel semble déterminé à contrecarrer les ambitions d’AMD de s’emparer de la couronne du PC.

Commentaire