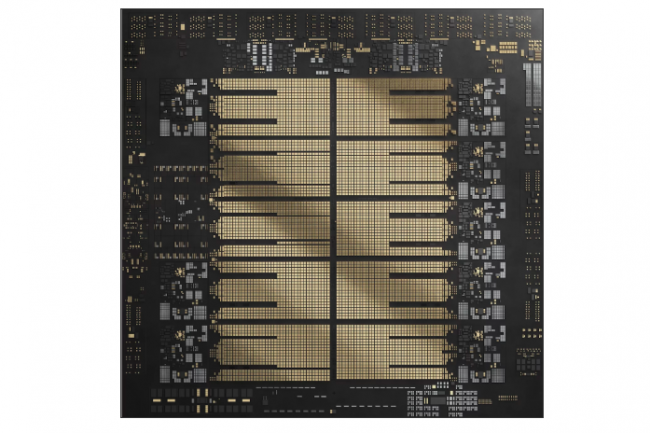

La prochaine génération de mainframes Z et LinuxONE sera équipée du processeur Telum 2 et d'un accélérateur visant à améliorer les performances de l'IA et d'autres charges de travail à forte intensité de données. Le processeur Telum 2 dispose d'une plus grande capacité de mémoire et de cache que la génération précédente et intègre une unité de traitement des données (DPU) spécialisée dans l'accélération des entrées-sorties, ainsi que des capacités d'accélération de l'intelligence artificielle sur la puce. Développé à l'aide de la technologie Samsung 5 nm, le Telum 2 dispose de huit cœurs haute performance cadencés à 5,5 GHz. Il comprend une augmentation de 40 % de la capacité de cache sur la puce, avec des L3 et L4 virtuels passant respectivement à 360 Mo et 2,88 Go. « La puissance de calcul de chaque accélérateur devrait être multipliée par quatre et atteindre 24 milliards d'opérations par seconde (Tops). Mais les Tops à eux seuls ne disent pas tout », ont écrit Christian Jacobi, Fellow et CTO Systems Development, et Elpida Tzortzatos, Fellow et CTO de z/OS et AI sur IBM Z et LinuxONE chez IBM, dans un blog sur le processeur.

« Il s'agit de la conception architecturale de l'accélérateur et de l'optimisation de l'écosystème de l'IA qui se trouve au-dessus de l'accélérateur. Lorsqu'il s'agit d'accélérer l'IA dans des charges de travail d'entreprise de production, une architecture adaptée est importante. Telum 2 est conçu pour permettre aux modèles d'exécution de côtoyer les charges de travail d'entreprise les plus exigeantes, tout en fournissant des inférences à haut débit et à faible latence ». Dans une configuration maximale, les futurs systèmes IBM Z peuvent être équipés de 32 processeurs Telum2 et de 12 cages IO. Chaque cage peut accueillir jusqu'à 16 emplacements PCIe, ce qui permet au système de prendre en charge jusqu'à 192 cartes PCIe. Des protocoles d'E/S personnalisés amélioreront la disponibilité, le contrôle des erreurs et la virtualisation afin de répondre aux exigences de bande passante massive et d'assurer la redondance et le multi-pathing pour la protection contre les scénarios de défaillances multiples simultanées. « De nouvelles primitives de calcul ont également été intégrées pour mieux prendre en charge les modèles de langage volumineux au sein de l'accélérateur. Elles sont conçues pour prendre en charge une gamme de plus en plus large de modèles d'IA pour une analyse complète des données structurées et textuelles », écrivent Christian Jacobi et Elpida Tzortzatos.

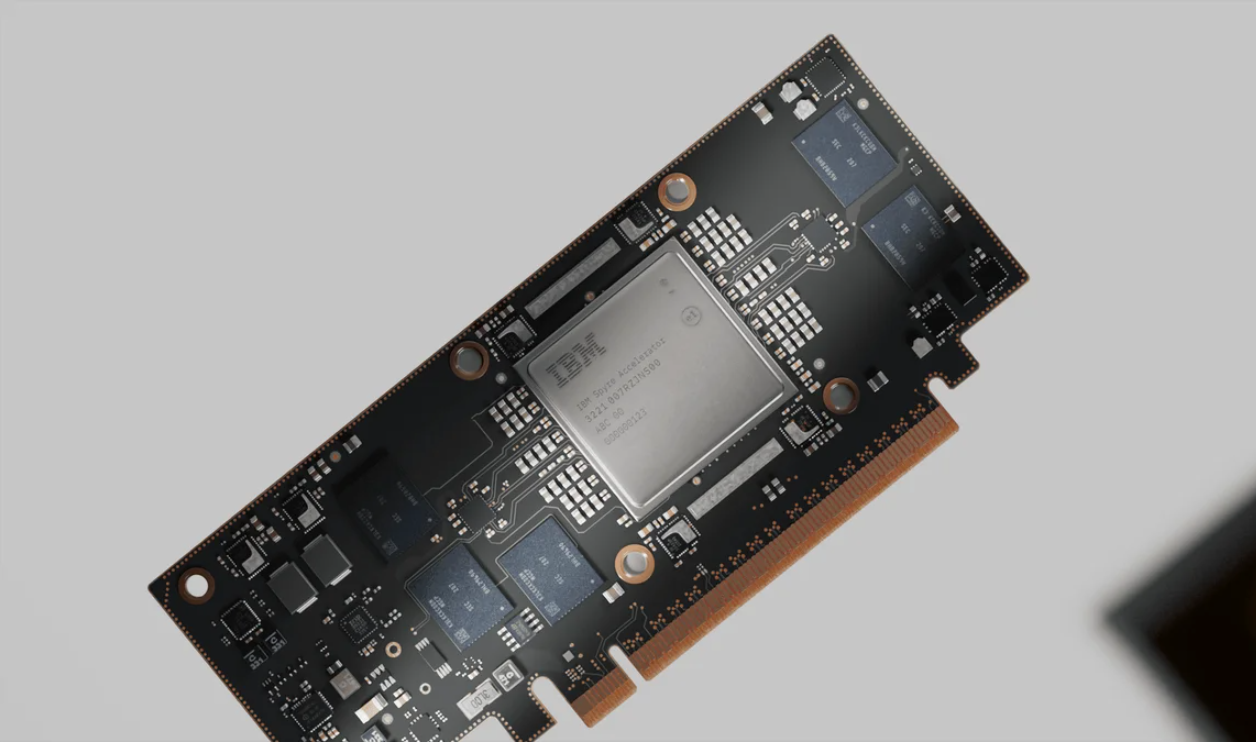

L'accélérateur IA Spyre embarque 32 cœurs d'accélérateur individuels et contient 25,6 milliards de transistors. Les cartes peuvent être regroupées - par exemple, un groupe de 8 cartes ajoute 256 cœurs d'accélération supplémentaires à un seul système IBM Z.

Un DPU revu sur la puce Telum II

Le premier processeur Telum d'IBM, introduit en 2021, comprenait un accélérateur IA intégré pour l'inférence. Avec le Telum 2, big blue a considérablement amélioré l'accélération IA, avec l’ajout d’un DPU spécialisé pour booster les entrées-sorties. Selon le fournisseur, le DPU simplifie les opérations du système et peut améliorer les performances des composants clés. Du point de vue du réseau et des E/S, l'un des avantages de cette approche est de passer d'une carte de connexion par fibre optique (FICON) à 2 ports à une carte à 4 ports et de consolider les offres Open Systems Adapter (OSA) Express - le package du mainframe pour le réseau via une variété de protocoles de réseau - et RDMA over Converged Ethernet (RoCE) Express au niveau du système, selon Michael Becht, ingénieur en chef et architecte pour les canaux E/S d'IBM Z, et Susan M. Eickhoff, directrice du développement du processeur IBM Z. « Ce changement, disponible à partir de la prochaine génération d'IBM Z dans la première moitié de 2025, permettra aux clients de conserver la même configuration d'E/S dans une empreinte plus petite, afin de réduire l'espace au sol du centre de données alors qu'ils mettent à niveau et modernisent leur infrastructure », ont écrit Michael Becht et Susan Eickhoff dans un blog.

Accélérateur IBM Spyre

En complément du processeur Telum 2, le Spyre Accelerator - également gravé en 5 nm - offre des capacités de calcul supplémentaires en matière d'intelligence artificielle. Sur une carte PCIe, le Spyre contient 1 To de mémoire et 32 unités de traitement pour l’IA qui partageront une architecture similaire à l'accélérateur IA intégré dans la puce Telum 2, selon Christian Jacobi et Elpida Tzortzatos : « Plusieurs accélérateurs Spyre peuvent être connectés au sous-système E/S d'IBM Z via PCIe. La combinaison de ces deux technologies peut entraîner une augmentation substantielle de la quantité d'accélération disponible ». Ensemble, le Telum 2 et l'accélérateur Spyre représentent un point d'inflexion clé pour le mainframe, selon Steven Dickens, conseiller technologique en chef du Futurum Group. « Le fait que toutes ces innovations en matière de puces et d'IA proviennent d'IBM et soient déployées sur des mainframes est à peu près aussi innovant et important que possible pour les clients d'entreprise », a déclaré M. Dickens.

Charges de travail mainframes et IA

Alors que les technologies de processeur améliorent leur support de l'IA et des charges de travail associées, big blue a d'autres applications et cas d'utilisation à forte intensité de transactions qui bénéficieront également d'une augmentation des performances et de l'efficacité énergétique, selon Tina Tarquinio, vice-présidente de la gestion des produits pour IBM Z et LinuxONE. « Les cas d'utilisation de Spyre et de l'accélérateur couvrent vraiment tous les cas d'utilisation métier auxquels vous pouvez penser », a déclaré Mme Tarquinio. « IBM l'utilise pour accélérer et utiliser l'IA afin d'aider nos demandes et fonctions internes en matière de ressources humaines, par exemple. La prochaine génération d'IBM Z conservera son leadership en matière de résilience, et nous disposons d'une disponibilité de huit neuf, en plus d'être le seul système à sécurité quantique existant. » Les analystes ont également souligné que les prochains mainframes basés sur Telum 2 auront un impact non seulement sur le développement de l'IA en entreprise, mais aussi sur d'autres applications, telles que la gestion des bases de données et les environnements cloud distribués ou hybrides. « Il suffit de regarder les caractéristiques de base de ces appareils en tant que serveurs - ce seront simplement des bêtes d'E/S », a déclaré M. Dickens. « Les clients pourront faire tourner de grosses bases Oracle, des MongoDB ou d'autres applications critiques de manière beaucoup plus efficace. Les entreprises pourront retirer les charges de travail transactionnelles du processeur principal et transférer ces traitements vers l'accélérateur pour l'apprentissage automatique, l'IA ou l'évaluation et le traitement de l'IA générative, a déclaré M. Dickens, ce qui est logique du point de vue opérationnel et évolutif.

« Outre la génération de code, cette plateforme d'IA évolutive pour mainframe (puce/carte/logiciel) conviendrait à un certain nombre d'applications, notamment les évaluations de crédit, la détection des fraudes, la conformité, les règlements financiers, ainsi que le traitement et la simulation de documents », a déclaré Patrick Moorhead, fondateur, CEO et analyste en chef de Moor Insights & Strategy. « Si vous êtes une entreprise et que vous possédez un mainframe, vous l'utilisez probablement pour des applications critiques qui requièrent le plus haut niveau de résilience et de sécurité. Auparavant, dans le domaine de l'IA, les entreprises déplaçaient les données de l'ordinateur central vers un serveur GPU, les traitaient, puis les renvoyaient sur le mainframe », explique M. Moorhead. « Ce n'est ni efficace ni rapide et c'est moins sûr pour des applications telles que les évaluations de crédit, la détection des fraudes et la conformité. M. Jacobi d'IBM a également expliqué comment la sécurité du code et la conformité bénéficieront de la nouvelle prise en charge de l'IA. « De nombreux clients exécutent des dizaines de millions de lignes de code, voire des centaines de millions de lignes de code dans leurs applications, et ils sont très soucieux de la sécurité et sensibles à la base de code », a déclaré M. Jacobi. « La base de code elle-même est en quelque sorte un processus commercial codifié sur la façon de gérer une compagnie d'assurance ou une banque. Il s'agit donc bien sûr d'une propriété intellectuelle très précieuse pour eux. « Lorsque les clients font de l'IA sur ce type de structures de code, ils préfèrent le faire directement dans l'environnement sécurisé de l'ordinateur central, plutôt que d'effectuer cette analyse ailleurs. C'est désormais possible », a déclaré M. Jacobi.

En 2025 sur les prochains mainframes

« Avec le Spyre, nous pouvons regrouper jusqu'à huit cartes pour obtenir la taille de mémoire et la capacité de calcul nécessaires pour exécuter des charges de travail GenAI sur ce code. Et nous intégrerons cela à nos produits de niveau supérieur comme Watson Code Assistant pour Z avec des modèles optimisés qui sont entraînés et tunés pour avoir les connaissances nécessaires pour faire une sorte de refactorisation de code mainframe et d'explication de code mainframe », a déclaré M. Jacobi. Le Telum 2 sera le processeur central des plateformes Z et LinuxONE de prochaine génération attendues en 2025, selon IBM. L'accélérateur Spyre, actuellement en avant-première technique, devrait également être disponible en 2025.

Commentaire