L'analytique en temps réel, c'est la cible visée par Intel avec ses derniers processeurs Xeon E7 v3 qui arriveront sur le marché courant juin dans les premiers serveurs équipés. Dell a déjà annoncé les siens, ceux des autres constructeurs partenaires arriveront dans la foulée. Intel travaille avec 16 d'entre eux, parmi lesquels HP, Bull, Cisco, Lenovo, Fujitsu, Nec et Hitachi, mais aussi SGI, Oracle, Huawei, Supermicro, ZTE, PowerLeader, Inspur et Sugon.

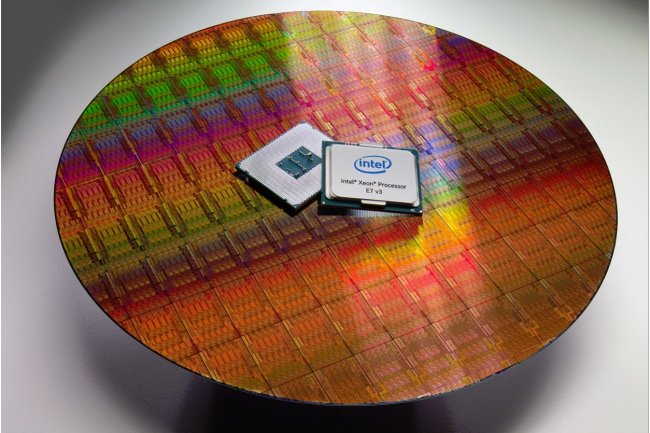

Hier, à Paris, l'équipe française d'Intel a relayé l'annonce de ces puces conçues pour exploiter des applications d'entreprises exigeantes, exploitant typiquement des bases de données relationnelles telles qu'Oracle ou IBM DB2. Elles sont livrées en douze références, réparties entre les versions à 4 ou 8 sockets : Xeon E7-48xx v3 ou E7-88xx v3. Il s'agit donc d'une gamme simplifiée par rapport aux 19 références des Xeon E7 v2. Avec ces processeurs, l'architecture Haswell arrive sur les systèmes multiprocesseurs alors que les E7 v2 étaient basés sur Ivy Bridge EX. Gravées en 22 nm, les nouvelles puces apportent une performance de 20% supérieure à la génération précédente en termes d'intégration de coeurs avec 18 coeurs et 36 threads par socket (contre 15 et 30 pour les Xeon E7 v2), ce qui permet de monter jusqu'à 144 coeurs sur les E7-8870, E7-8880 et E7-8890 (18 coeurs par socket sur 8 sockets). La mémoire cache de niveau 3 peut aller jusqu'à 45 Mo (37,5 précédemment). Sur les tests OLTP, l'amélioration de performances atteint 35%.

Destinée aux applications in-memory, supporte la DDR4

« A côté de l'usage traditionnel, c'est-à-dire les bases de données performantes utilisées pour les entrepôts de données, on voit émerger de nouveaux usages comme le in-memory, très à la mode, notamment avec SAP HANA », a indiqué hier Stanilas Odinot, consultant technique de la division Entreprise, investi dans la collaboration avec les OEM et l'avant-vente. « Avec SAP, nous participons activement au développement autour de HANA », a-t-il cité en exemple. Sur un processeur 4 sockets, on peut monter à 6 To de mémoire, donc 12 To sur 8 sockets. Cette génération supporte la DDR4 en plus de la DDR3, les OEM ayant la flexibilité de proposer l'une ou l'autre selon les applications qu'ils veulent proposer. La DDR4 présente un double avantage. Elle offre un petit gain de bande passante supplémentaire (+16%) et améliore de 50% l'efficacité énergétique. « Sur un 16 sockets, cela commence à jouer », a pointé Stanilas Odinot.

Sur les 12 puces de la famille Xeon E7 v3, Intel propose en entrée les E7-4809 (8 coeurs, fréquence 2 GHz, 20 Mo de cache L3) et 4820 (10 coeurs, 1,9 GHz, 25 Mo L3), puis les E7-4830 (12 coeurs, 2,1 GHz, 30 Mo L3) et E7-4850 (14 coeurs, 2,2 GHz, 35 L3). Ces puces 4 sockets consomment 115 W. Viennent ensuite les processeurs à 8 sockets : du E7-8860 au E7-8890 (16 ou 18 coeurs, 2,2 GHz, 40 à 45 Mo L3, 140 W ou 165 W). Les versions 88xx comportent aussi le 8867 (16 coeurs) qui monte à 2,5 GHz, le 8891 (10 coeurs, 2,8 GHz), le 8893 (4 coeurs et 3,2 GHz) et une version basse consommation à 115 W, le 8880L à 18 coeurs, 2 GHz et 45 Mo L3.

Sur les aspects haute disponibilité, Intel recourt à des technologies de résilience (« très haut dans le système »). Pour les capacités hot-plug par exemple, Intel travaille avec de nombreux fournisseurs d'OS, mais il faut que ce soit pris en compte par les OEM, rappelle le consultant technique. « On doit pouvoir aussi garantir l'intégrité des données », souligne-t-il en rappelant que c'est l'un des éléments forts du Xeon 7. Parmi les nouvelles instructions du processeur figure l'introduction des capacités TSX (Transactional Synchronization Extensions) qui permettent d'apporter plus de performances, notamment sur SAP HANA, en les activant ou en les désactivant. Elles vont pouvoir être utilisées par les éditeurs de logiciels sur le multithreading et peuvent apporter 40% de performances en plus car on bloque moins la mémoire. Une possibilité typiquement demandée par les éditeurs de bases de données. Mais encore une fois, rappelle le consultant technique de la division Entreprise d'Intel, c'est activable si le fabricant du serveur le laisse dans le BIOS en option. « Ce sera comme d'habitude à la disposition des OEM de le désactiver et voir s'il y a un impact sur la performance », a-t-il précisé.

De plus en plus de demandes pour des puces personnalisées

Autre apport, avec les instructions AVX 2.0, les registres sont passés à 256 bits sur les flottants et les entiers, ce qui n'était pas le cas sur les générations précédentes, a indiqué Stanislas Odinot. Avec l'arrivée du Cache Monitoring, exploitable par les principaux hyperviseurs, les applications peuvent voir le taux d'engorgement du cache de niveau 3. « Typiquement, on peut voir si l'une des VM est plus bruyante que les autres et faire des règles d'arbitrage pour la déplacer car elle gêne les performances de toutes les autres ». Plus atypique, la technologie de VMCS (Virtual Machine Control Structure) shadowing, plutôt destinée aux acteurs de l'IaaS, remonte cet état à l'intérieur d'une VM. « C'est un usage particulier et ce n'est pas la technologie la plus utilisée, mais nous avons eu cette demande de la part de nos clients du cloud », a expliqué Stanislas Odinot.

Les différentes versions de Xeon E7 v3 répondent à des problématiques distinctes. Les utilisateurs de bases de données dont les licences logicielles sont facturées au nombre de coeurs opteront peut-être pour des puces intégrant moins de coeurs, rappelle le consultant d'Intel. Les entreprises qui veulent limiter la consommation d'énergie se tourneront vers la version 18 coeurs à 115 W, plus chère mais qui consomme moins. Autre exemple, les utilisateurs d'applications HPC miseront sur un maximum de coeurs en montant la fréquence. A partir de ses gammes de processeurs, Intel fait aussi des puces personnalisées (il l'a déjà fait pour Oracle, par exemple). Il n'y en a pas encore eu sur ceux-ci apparemment, mais il y a de plus en plus de demandes dans ce domaine, selon S.Odinot.

Petite erreur dans la phrase: "les registres sont passés à 256 bits"

Signaler un abusC'est du 512 bits.