La technologie EMIB (Embedded Multi-Die Interconnect Bridge) de la puce Kaby Lake-G d'Intel avait justifié le partenariat avec AMD. La future puce Lakefield exploitera la technologie des matrices empilées Foveros d'Intel. Désormais, le fondeur combine les technologies EMIB et Foveros pour produire ce que le fondeur appelle le « co-EMIB », avec une interface ODI plus avancée. L’association de ces deux technologies « amélioreront les performances, la puissance et l'espace au niveau du produit tout en permettant de repenser complètement l'architecture du système », a déclaré la firme dans un article de blog. Chacune témoigne des progrès accomplis dans l’assemblage et la connexion des puces, plus que de modifications sur le silicium sous-jacent ou la microarchitecture globale.

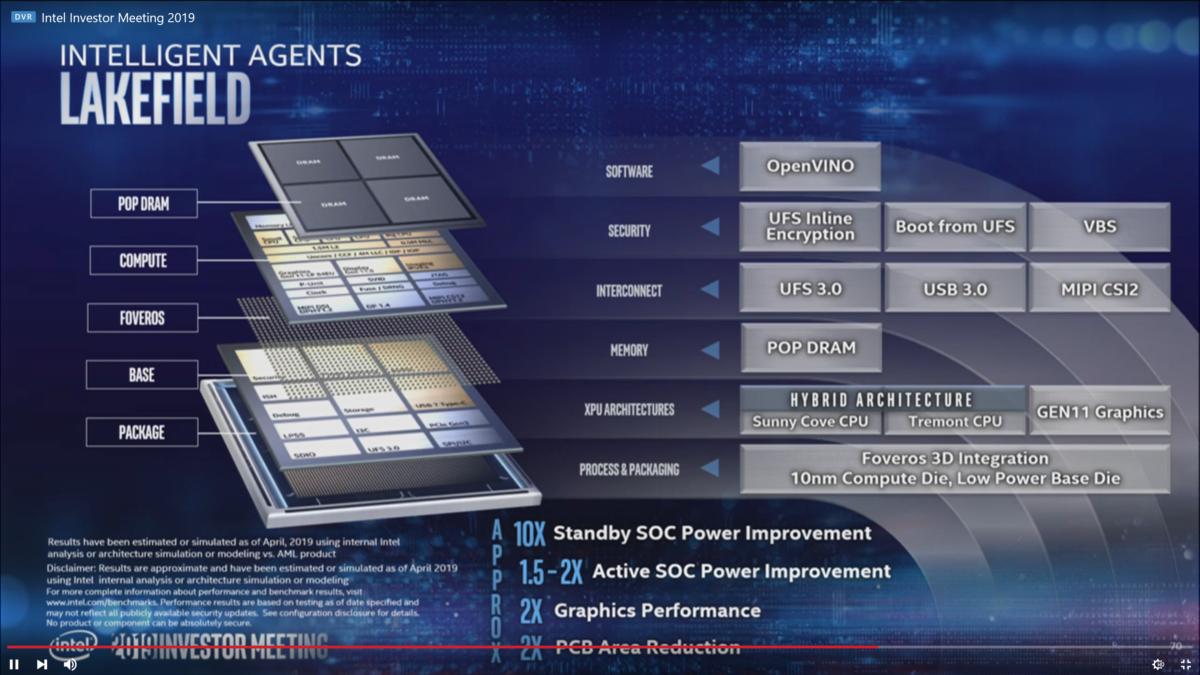

On ne sait pas exactement à quel moment l'une ou l'autre de ces technologies sera mise sur le marché, ni quels impacts elles auront sur les produits. Mais nous avons déjà une idée de ce que l’EMIB et Foveros peuvent apporter. La technologie EMIB (Embedded Multi-Die Interconnect Bridge) présente dans la puce Kaby Lake-G a été à l’origine du partenariat conclu en 2017 entre AMD et Intel, donnant naissance au concept des « chiplets » mondialement reconnu. Quant à la technologie Foveros, il s’agit d’un empilage de puces qui sera utilisé pour la prochaine puce Lakefield d’Intel. Foveros empiles des puces Core et Atom pour les applications à faible consommation d’énergie.

Les concepts EMIB et Foveros, indispensables pour Intel

Pourquoi le fondeur a-t-il besoin des technologies EMIB ou Foveros ? Parce que ça lui coûterait tout simplement trop cher de charger un système de puces entier sur une seule matrice de silicium. Non seulement les puces peuvent être fabriquées à moindre coût en utilisant d'anciens processus au silicium, mais les défauts de fabrication peuvent rendre cette énorme matrice monolithique inutilisable. Une multitude de puces plus petites et moins chères - reliées entre elles par des interconnexions haut débit - est un compromis efficace. Et EMIB et Foveros sont à même d’y contribuer.

Le bridge d'interconnexion multi-matrice intégré, ou EMIB, permet de relier les broches I/O d'une puce aux broches I/O d'une autre puce, en assurant une interconnexion processeur-à- processeur optimisée qui permet à la puce de travailler à deux niveaux sans trop de perte de performance. Cela permet aussi à un concepteur de puces comme Intel de faire des économies, puisqu’il peut réutiliser des technologies de fabrication plus anciennes et moins chères, et réserver son processus à 10nm plus rapide à la fabrication d'autres cœurs. Et les EMIB peuvent les relier ensemble.

Des amalgames de puces

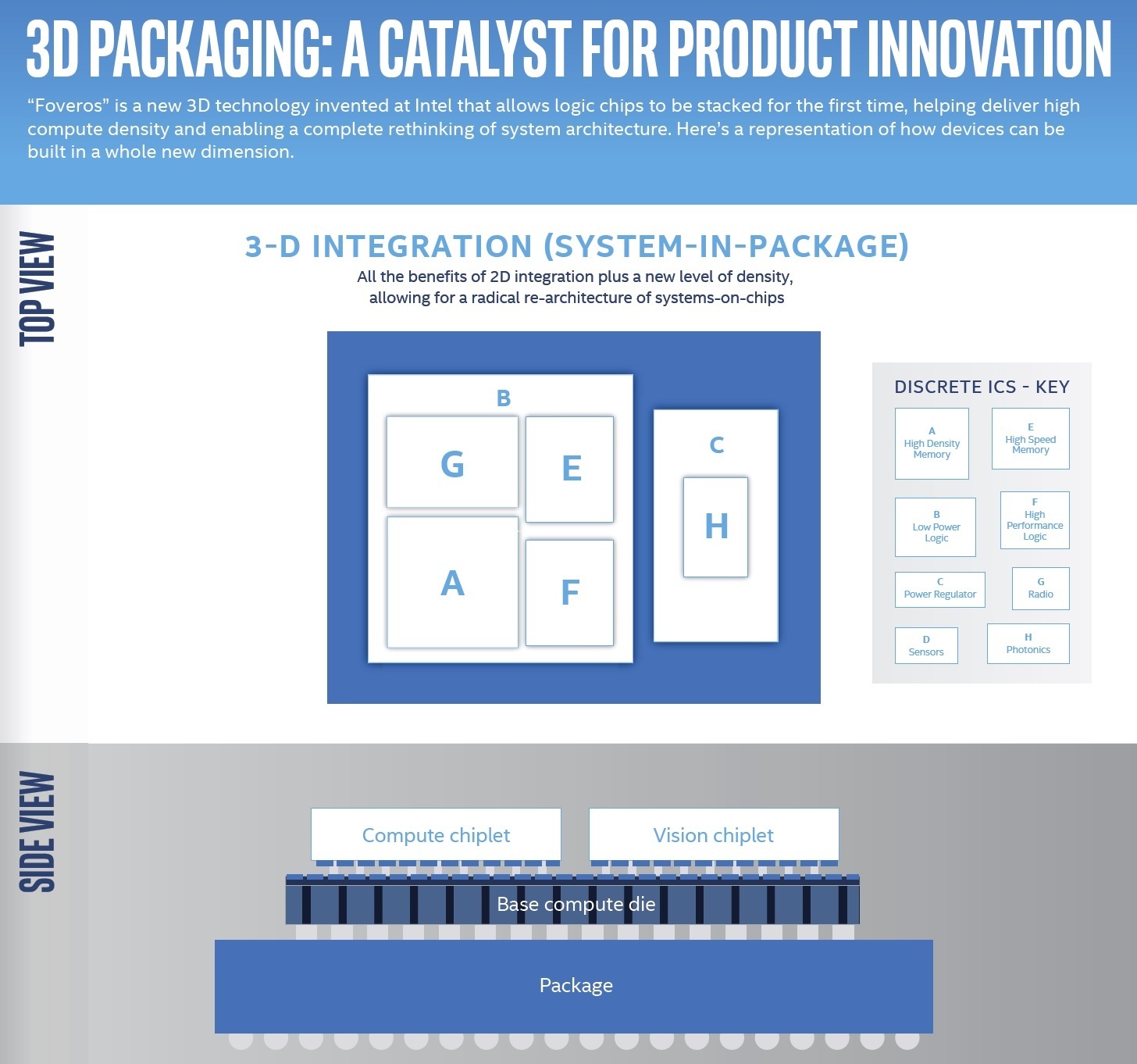

En 2018, Intel avait présenté sa technologie d'empilage Foveros, qui permet d’étendre les puces verticalement. Avec Foveros, les concepteurs peuvent empiler un CPU basse consommation sur un autre, et même compléter l’ensemble avec de la mémoire. Au mois de janvier, Intel avait déclaré que sa future puce Lakefield utiliserait l'interconnexion Foveros. En mai, le fondeur a expliqué plus en détail que la puce combinerait les architectures Sunny Cove et Tremont.

À la fin de l'année dernière, Intel a expliqué le fonctionnement de la technologie Foveros. (Crédit : Intel)

Co-EMIB et ODI : des extensions vers le haut, vers le bas et vers l'extérieur

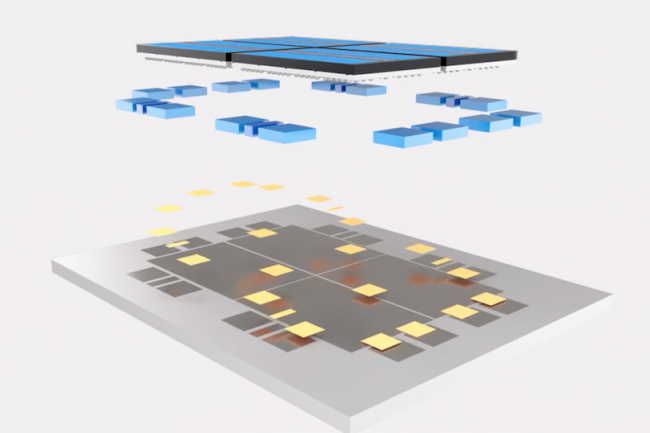

Si vous avez compris comment fonctionnent les technologies EMIB et Foveros, vous aurez une meilleure idée de la façon dont co-EMIB combine les deux. Selon Intel, « la technologie co-EMIB permet l'interconnexion horizontale de deux ou plusieurs éléments Foveros, tout en restituant la performance d'une seule puce ». Elle permet également de connecter de la mémoire et même un circuit intégré logique/analogique à large bande passante et à basse énergie. En quelque sorte, la puce Foveros est empilée comme les planchers d’un gratte-ciel, la co-EMIB servant de passerelle entre deux piles Foveros différentes.

La technologie co-EMIB d’Intel fonctionne un peu comme une passerelle entre deux empilements Foveros. (Crédit : Ashok Prabhakaran/Flickr)

Intel a également évoqué ce qui semble être une version optimisée de la combinaison Foveros-EMIB : l'interconnexion omnidirectionnelle, ou ODI. « La puce supérieure peut communiquer horizontalement avec d'autres puces, comme dans le cas de l'EMIB », a déclaré Intel. « Elle peut aussi communiquer verticalement par les vias - les connexions métalliques entre les différentes couches de substrat - de silicium traversant (TSV) dans la matrice de base sous-jacente, comme Foveros ». Toujours selon Intel, ces grands vias peuvent également permettre de transférer de l'énergie vers le substrat, quel que soit l’élément logique de la matrice supérieure elle-même. Intel a élargi les vias au-delà de la normale pour faire en sorte d’augmenter la circulation de l’énergie en raison d’une moindre résistance.

Enfin, le fondeur a révélé ce qu'il appelle le MDIO, une interface substrat-à-substrat. Lors du Semicon West organisé à San Francisco du 9 au 11 juillet, Intel a déclaré que le MDIO fournirait une vitesse de 5,4 Gb/s au niveau du pin en précisant que son lancement était prévu en 2020. Aucune de ces technologies n'aura d'impact direct sur le marché du PC. Mais elles offrent à Intel encore plus de flexibilité dans ses conceptions et apportent de nouvelles options pour améliorer encore plus les performances en jouant sur la combinaison des éléments logiques. Certes, la loi de Moore ralentit, mais les utilisateurs attendent toujours des améliorations. Intel et ses concurrents doivent donc faire preuve de créativité !

Commentaire