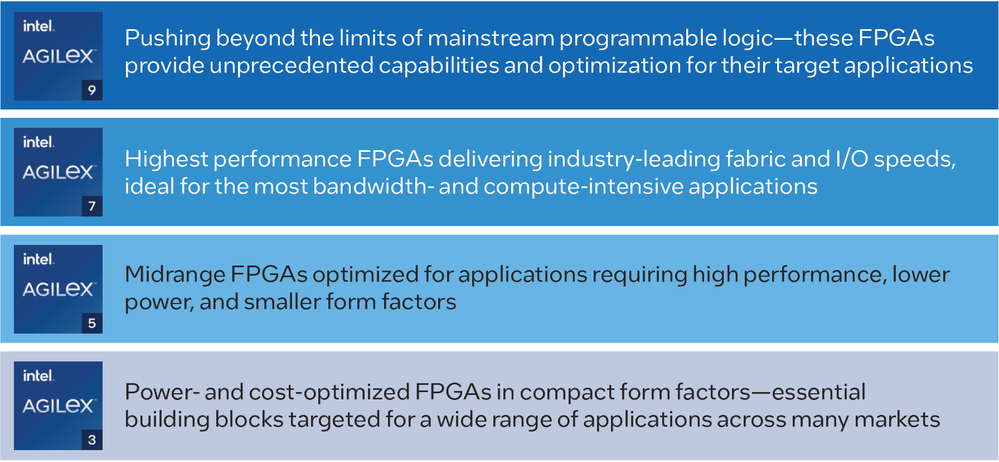

À l’occasion de son événement Innovation à San José, les 19 et 20 septembre derniers, Intel a actualisé sa gamme FPGA avec des offres à coûts optimisés, publié sa pile logicielle FPGA en open source et dévoilé une plateforme processeur reposant sur l'architecture RISC-V. Le premier des produits présenté est la famille Agilex 3, des FPGA optimisés en termes de performances et de coût, disponibles dans des formats compacts. Agilex suit la même convention de dénomination de produit que les puces pour PC Core : 3 est l’extrémité la plus basse du spectre de performances, suivi des séries 5, 7 et 9 par ordre croissant.

La famille Agilex 3 comprendra plusieurs branches : les séries B et C. Les FPGA de la série B ont une densité d'E/S plus élevée dans des facteurs de forme plus petits et une consommation inférieure à celle des autres FPGA du fondeur de Santa Clara. Ces circuits programmables sont destinés à la gestion des cartes et des systèmes, y compris les applications de gestion de plate-forme serveur (PFM). Les FPGA de la série C offrent des fonctionnalités supplémentaires pour une gamme de dispositifs logiques programmables complexes (CPLD) et d'applications sur les marchés verticaux.

La famille de circuits FPGA Agilex se compose de quatre branches. (Crédit Intel)

Intel a également annoncé l'Agilex 5 E-Series dans le cadre de son programme d'accès anticipé, avec des échantillons disponibles pour les clients privilégiés à partir du quatrième trimestre 2023 et une disponibilité plus large au premier trimestre 2024. Ces ajouts à la famille Agilex 5 sont destinés à offrir de meilleures performances par watt que les FPGA concurrents, grâce à une amélioration du processus de fabrication. Les FPGA Agilex 7 avec R-Tile, annoncés pour la première fois en mai dernier, sont désormais disponibles. Ils disposent d'une bande passante reposant sur PCIe 5.0 et CXL 2.0, jusqu'à quatre fois supérieure par port par rapport aux FPGA concurrents, selon Intel.

Passage en open source

Côté software, le fondeur met à disposition son logiciel Open FPGA Stack (OFS) en open source. OFS est conçu comme un cadre commun pour le développement de FPGA, offrant à la fois des bibliothèques de codes de référence et des pilotes de noyau open source en amont pour Linux. OFS prend en charge à la fois Agilex et la gamme de FPGA Stratix 10.

Une autre annonce concerne le développement d’accélérateurs IP autour de la puce Nios V, basée sur l'architecture ouverte RISC-V. Le Nios V/c est un microcontrôleur compact conçu pour compléter les implémentations FPGA. Il ciblera également tous les équipements pris en charge dans le logiciel de conception de dispositifs logiques programmables Quartus Prime Pro, a indiqué Intel. Enfin, le fournisseur a lancé la première unité de traitement d'infrastructure (IPU) F2000X (mieux connue sous le nom de SmartNIC). Les premiers adaptateurs accessibles au public proviendront de Napatech, l'un des principaux fournisseurs de SmartNIC et d'IPU.

Commentaire