La 68e édition du dernier salon IEDM (International Electron Devices Meeting) 2022 à San Francisco a marqué le 75e anniversaire du transistor. Il a aussi été l'occasion pour Intel de lever le voile sur ses prochaines évolutions en matière de conception de puces. « Le groupe de recherche sur les composants d'Intel a montré son engagement à innover dans trois domaines clés pour poursuivre la loi de Moore : la nouvelle technologie de conditionnement de liaison hybride 3D pour permettre une intégration transparente des puces, des matériaux 2D ultra-fins pour installer plus de transistors sur une seule puce et d'autres possibilités en matière d'efficacité énergétique et de mémoire pour une informatique plus performante », a expliqué Intel.

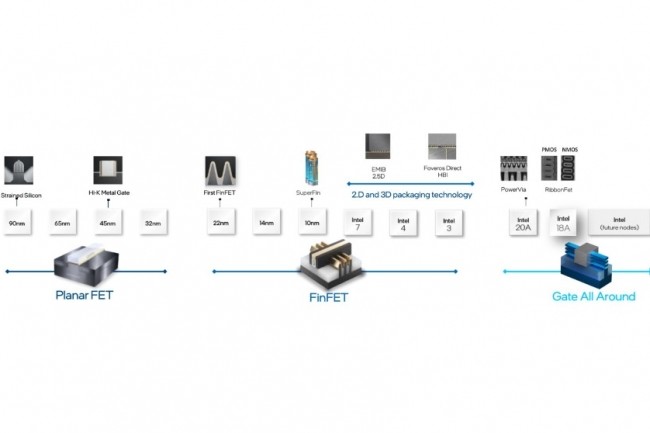

Le fondeur américain affiche ainsi de grandes ambitions avec une amélioration escomptée de densité multipliée par 10 au point d'atteindre la barre du billion de transistors sur une puce à horizon 2030. « Les innovations matérielles d'Intel ont également identifié des choix de conception pratiques qui peuvent augmenter la densité des transistors dans les puces en utilisant un matériau de seulement 3 micron d'épaisseur, permettant à l'entreprise de continuer à évoluer au-delà du RibbonFET », a précisé la firme. Une évolution technologique au niveau de la conception du processeur qui permet au fondeur d'entrer dans l'ère l'angström, évoquée l'an dernier par son CEO Pat Gelsinger.

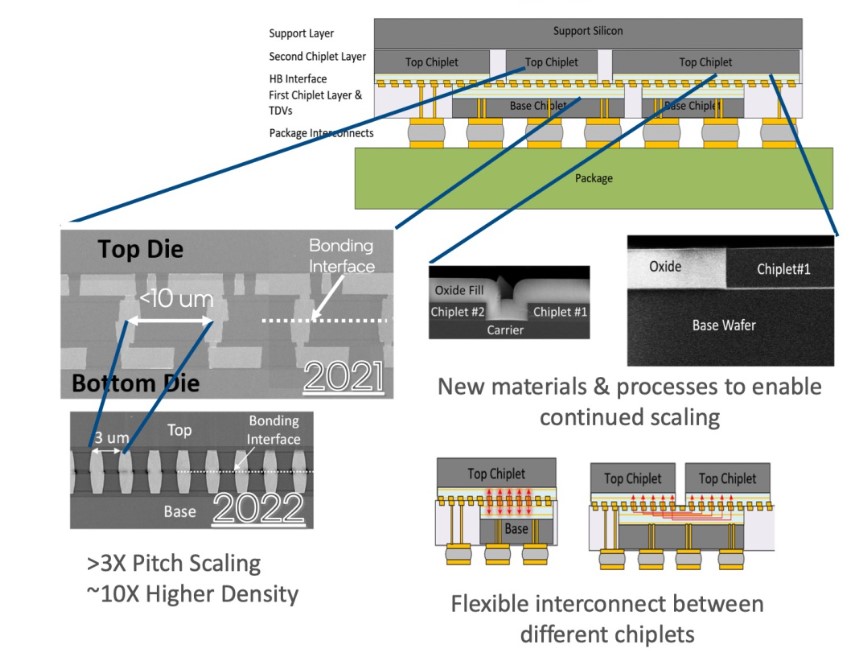

La technique de liaison hybride QMC doit permettre d'améliorer la densité d'interconnexion des futures puces Intel. (crédit : Intel)

Du Nitrure de Gallium pour faire bondir la performance des puces

Pour atteindre ces niveaux de performance, Intel compte s'appuyer sur une technique de liaison hybride QMC (quasi-monolithic chips) couplée à une architecture de transistors RibbonFET. Cette dernière marque le passage aux transistors gate-all-around (GAA) avec un empilement vertical des couches pour améliorer la gestion des flux et la circulation du courant électrique. La firme a ainsi présenté un premier cas d'usage basé sur des condensateurs ferroélectriques empilés pour concevoir des puces FeRAM afin de remplacer les mémoires flash de type NOR et SRAM.

Les chercheurs d'Intel travaillent également sur de meilleures façons de stocker les informations quantiques en tentant de résoudre les problèmes d'interconnexion qui peuvent les perturber. Cela passe en particulier sur la mise au point de dispositifs à base de Nitrure de Gallium (GaN) au coeur de la conception de la prochaine génération de composants électroniques. « Intel construit une voie viable vers des wafers GaN de 300 millimètres. Les percées d'Intel dans ce domaine démontrent un gain 20 fois supérieur par rapport au standard actuel de l'industrie et préfigure un niveau jamais atteint en termes de puissance et de haute performance », avance le fondeur.

Commentaire