Il reste de nombreux défis à relever pour faire progresser le champ de l’informatique quantique. Un immense chantier qui requiert les énergies combinées du monde académique et des industriels. Parmi les acteurs technologiques, AWS met en lumière cette semaine un article scientifique intitulé « Building a fault-tolerant quantum computer using concatenated cat codes », écrit par une équipe de l’AWS Center for Quantum Computing. Celui-ci décrit un schéma théorique pour un ordinateur quantique tolérant aux pannes avec une nouvelle approche de la correction d’erreur quantique (QEC). Dans un billet, deux des chercheurs, Patricio Arrangoiz-Arriola et Earl Campbell, présentent ces travaux.

Les algorithmes quantiques vont permettre de résoudre un large éventail de problèmes, tant dans la conception de nouveaux matériaux que dans la découverte de médicaments ou l’optimisation logistique. Mais ceux qui devraient avoir un avantage écrasant par rapport aux algorithmes classiques peuvent nécessiter des millions ou des milliards de portes quantiques. Malheureusement, ces dernières - qui sont les éléments constitutifs des algorithmes quantiques- sont sujettes aux erreurs, celles-ci pouvant s’accumuler rapidement et affecter les résultats. Il faut donc en améliorer la fiabilité. Actuellement, les meilleures portes quantiques subissent environ une erreur sur mille opérations, rappellent les chercheurs. Pour réduire les taux d’erreur, il faut des approches au niveau physique avec des méthodes telles que la QEC.

QEC active et QEC passive

L’article - qui s’adresse à un public de scientifiques - décrit une architecture qui combine des éléments de QEC active et de QEC passive ou autonome, expliquent les chercheurs. La première méthode de correction d’erreur réduit le taux d’erreur en codant de manière redondante dans un qubit logique utilisant de nombreux qubits physiques. Cela permet la détection et la correction d’erreur mais crée une surcharge matérielle importante. La deuxième méthode, passive ou autonome, est une approche contrastée, indiquent les chercheurs. « Cela nécessite de concevoir un système informatique physique qui possède une stabilité intrinsèque contre les erreurs », indiquent-ils en ajoutant que cela pourrait en théorie être réalisé en construisant un système topologique contenant des modes Majorana, mais cela n’a pas encore été démontré.

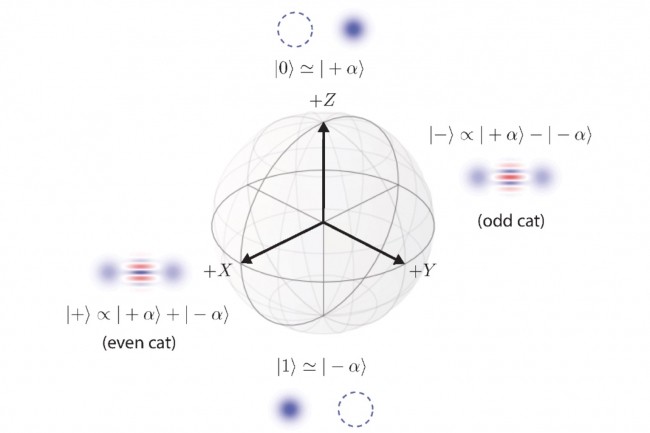

Dans l’architecture décrite, les informations sont stockées dans des oscillateurs harmoniques linéaires en utilisant le codage appelé cat qubit. « Nous avons envisagé une mise en oeuvre où les oscillateurs de stockage sont des nanostructures piézoélectriques qui présentent l’avantage d’être très compactes », indiquent MM Arrangoiz-Arriola et Campbell en précisant qu’il reste beaucoup à faire pour rendre les éléments piézoélectriques suffisamment cohérents et fiables. Le codage par cat qubit est conçu pour supprimer les erreurs bit-flip (changement d’état du bit). Les erreurs restantes sont prises en charge par une QEC active construite au-dessus des cat qubits, en utilisant des schémas de tolérance aux pannes adaptés aux propriétés du matériel.

Des modèles spécifiques au matériel considéré

« Dans notre article, nous avons construit des modèles d’erreur spécifiques au matériel considéré et avons utilisé ces modèles pour effectuer des simulations de la pile QEC », décrivent les chercheurs qui sont ensuite arrivés à une estimation de taille finale pour simuler le modèle Hubbard, algorithme quantique lié à la science des matériaux. « Nous avons calculé que cela nécessite 32 000 dispositifs d'interférence quantique supraconducteurs à threads asymétriques, SQUID », indiquent-ils. Les ATS (asmmetrically threaded SQUID) sont les composants supraconducteurs utilisés pour stabiliser les cat qubits. Le billet détaille les quatre idées-clés pour comprendre leur architecture : cat qubits et biased noise, stabilisation multiplexées et portes, QEC active et portes logiques quantiques.

Commentaire