Si dans le monde du PC la modularité a toujours existé, dans celui des puces, c’est plus compliqué. Mais l’heure est à l’ouverture comme le montre la création d’un consortium regroupant plusieurs sociétés dont Intel, ARM, Advanced Semiconductor Engineering (ASE), AMD, Qualcomm, Google Cloud, Meta, Microsoft, Samsung et TSMC (mais sans Nvidia et Apple). Ce groupe va travailler sur un standard nommé l’Universal Chiplet Interconnect Express, ou UCIe.

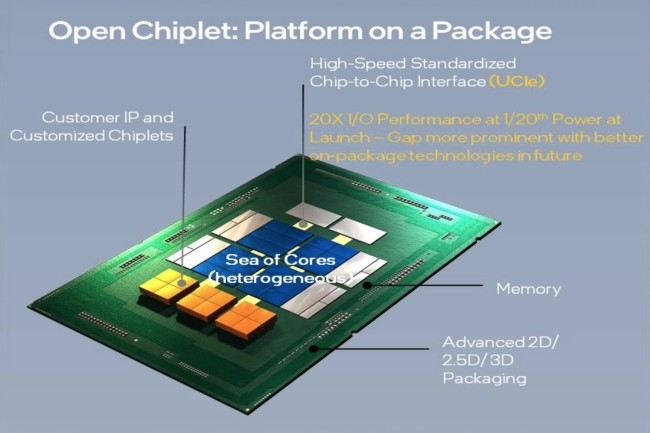

Ce dernier reprend le concept de chiplet qui vise à combiner et interconnecter différents modules disposant de leur propres die au sein de la puce et provenant de différents fournisseurs. AMD et Intel l’appliquent depuis des années : Intel avec ses connexions co-EMIB et ODI, par exemple, à l’origine de la puce hybride Alder Lake. Un partenariat d'ingénierie spécialisé entre AMD et Intel a également donné naissance à une puce Intel appelé Kaby Lake G, intégrant un GPU AMD.

Une interconnexion standardisée

Le consortium a pour ambition de « normaliser les interconnexions die-to-die » qui ne le sont pas aujourd’hui. Concrètement, l’UCIe transfère les données en utilisant soit le PCI Express existant, soit l'interface CXL (Compute Express Link) utilisée au sein des datacenters. En fait, un fournisseur de puces pourrait prendre le cœur de processeur d'une société, le cœur graphique d'une autre, et le modem WiFi ou 5G d'une troisième, et les assembler comme des blocs de LEGO en utilisant l’UCIe pour les interconnecter. Un peu comme si l’on insérait une carte graphique ou un SSD dans le connecteur PCI Express d'un PC. Mais avec l'UCIe, l’intégration se ferait simplement au niveau de la puce. Une première ébauche du standard en version 1.0 est déjà disponible.

Le prochain standard est également une sorte de reconnaissance : que les exigences des designs actuels dépassent tout simplement la capacité de l'industrie à les fabriquer physiquement. Pendant des décennies, l'industrie a essayé de concevoir des processeurs de PC tout-en-un regroupant un CPU, un GPU, des E/S, et plus encore, le tout sur une seule puce. Mais plus la taille des puces est grande, plus les chances d’erreurs de gravure sont élevées, avec le risque de rendre tout le composant inutilisable, ce qui représente donc une perte de valeur pour le fabricant et le concepteur.

Des puces de plus en plus modulaires

En effet, l’un des objectifs de l'UCIe est de se préparer au jour où les prochaines puces hybrides seront trop grandes pour être fabriquées avec les équipements lithographiques actuels. « Il serait plus facile pour l'ensemble de l'industrie, de construire des chiplets plus petits et de les assembler en faisant en sorte qu'ils se comportent comme une seule entité », a déclaré à HPCWire, Debendra Das Sharma, président de l'UCIe et chercheur principal chez Intel.

En théorie, l'UCIe signifierait que toute personne disposant des licences et de la propriété intellectuelle appropriées pourrait assembler des puces contenant les modules de différents fournisseurs. L'UCIe suggère également que des start-ups pourraient développer des chiplets spécialisés sur la base UCIe et les vendre à d’autres spécialistes des semi-conducteurs. En vérité, cette industrie dispose déjà de cette capacité depuis longtemps avec les FPGA d’entreprises comme Altera et Xilinx, toutes deux récemment acquises par Intel et AMD.

Commentaire