« L’architecture est une alchimie de logiciel et de matériel », a rappelé Raja Koduri, vice-président senior de l’activité Accelerated Computing Systems and Graphics Group chez Intel, à l’occasion de l'Architecture Day 2021 au cours duquel le fournisseur a donné des détails sur ses nouvelles architectures avec deux nouvelles générations de coeurs x86. En premier lieu, sur l’architecture hybride Alder Lake et l’ordonnanceur de tâches Thread Director, mais également sur Sapphire Rapids, la prochaine génération de processeurs Xeon Scalable pour les datacenters.

Alder Lake, le prochain microprocesseur d’Intel, marque un changement radical pour le fabricant de puces. C’est sa première architecture hybride qui combine des moteurs pour s’axer sur la performance tout en surveillant l’efficacité énergétique suivant le contexte des applications exécutées. Elle devrait être disponible dans le courant de cet automne, sous la forme d’une puce Core de 12ème génération. Intel va produire trois versions d’Alder Lake, l’une pour les desktops et les deux autres pour les ordinateurs portables. Le processeur apportera jusqu’à 16 coeurs et 24 threads. Cette architecture marque aussi l’arrivé de PCI Express 5 et de la mémoire DDR5.

Bâties sur la technologie Intel 7

Intel a co-désigné avec Microsoft un ordonnanceur de threads pour Windows 11. Les ordinateurs équipés d’Alder Lake pourront conjuguer les performances tout en préservant la durée de vie de la batterie, puisqu'Intel attribue à chaque coeur de processeur la tâche la plus appropriée et continue de progresser sur ce terrain. Alder Lake combine donc jusqu’à 16 coeurs : coeurs de performance (Intel utilise la terminologie P-Cores) et efficiency cores (ou E-Cores). Ces derniers sont utilisés pour les tâches de fond comme la synchronisation des emails. C’est une approche hybride qu’ARM utilise depuis de nombreuses années, de même que le processeur Lakefield d’Intel.

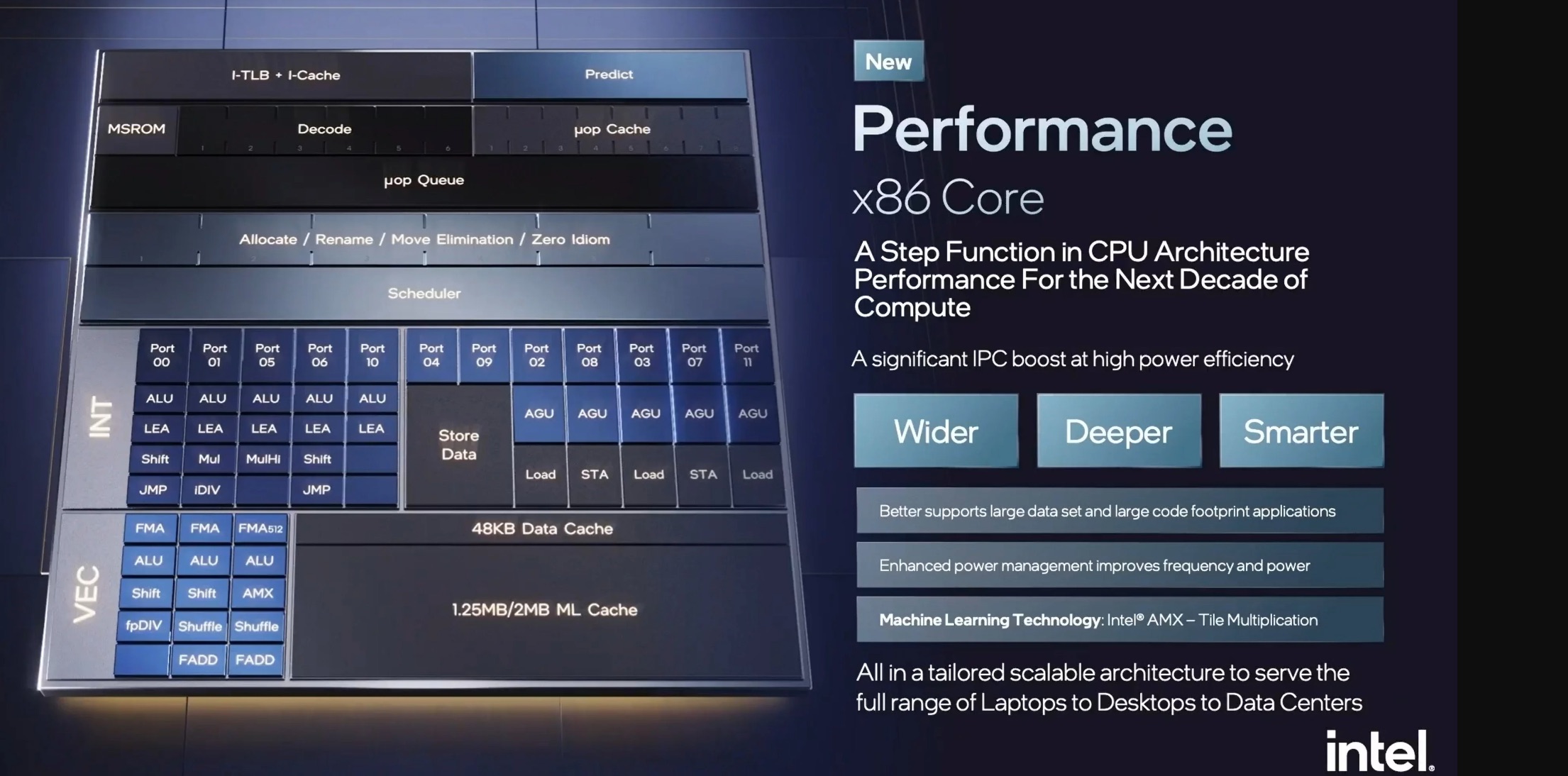

Un aperçu des coeurs de performance des Alder Lake. (agrandir l'image)

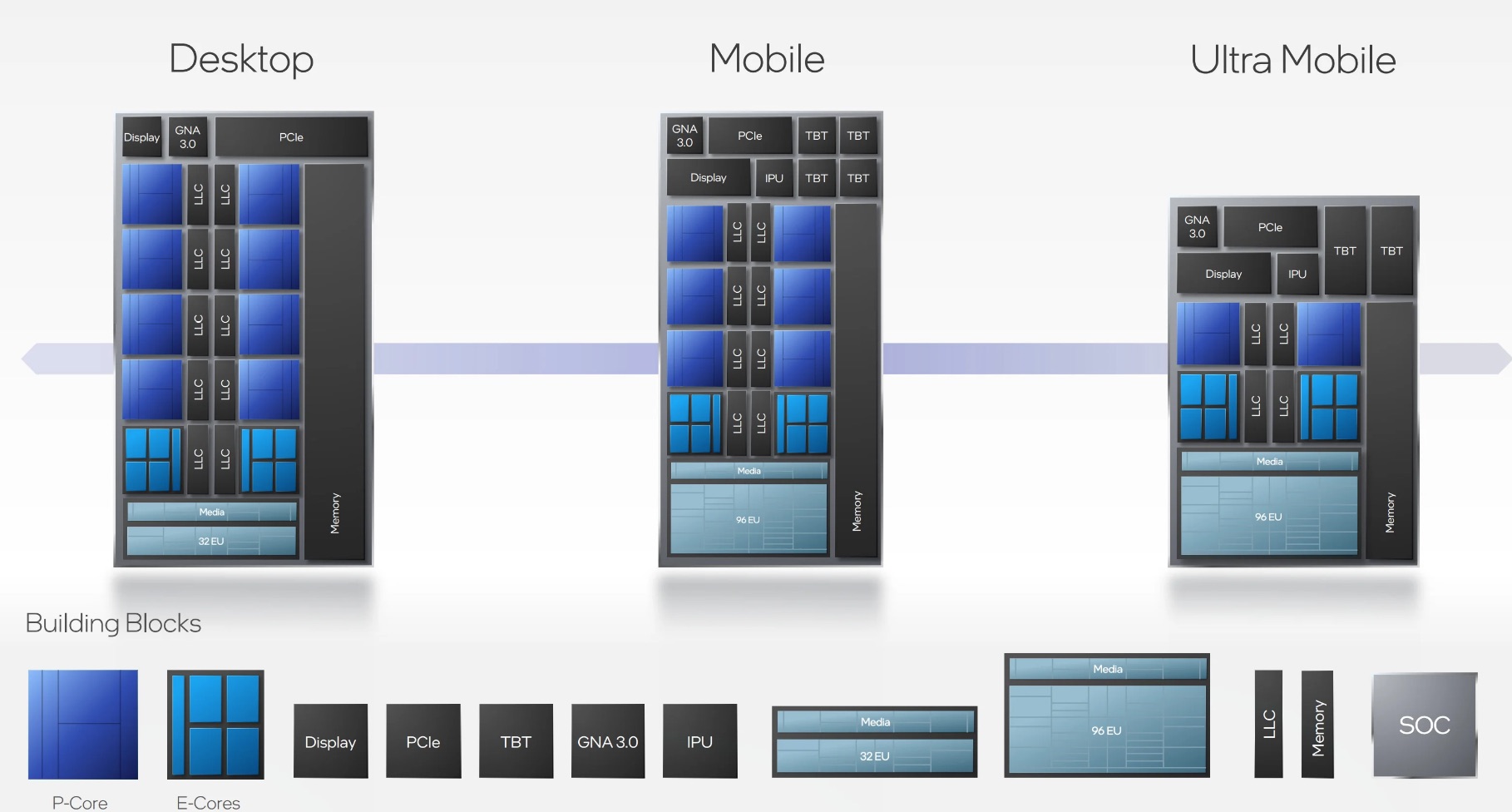

Les puces Alder Lake sont bâties sur la technologie Intel 7 (nouveau nom pour la technologie SuperFIN10 améliorée), pour des terminaux allant des tablettes 9 watts aux ordinateurs de bureau à 125 watts. Sur les P-Cores, la performance apportée est supérieure de 19% à celle de la puce Rocket Lake de 11ème génération pour desktop, indique Intel. Ces coeurs s’appuient sur le design CPU Cove d’Intel, tandis que les E-Cores utilisent le design Atom. Sur les trois versions d’Alder Lake prévues, celle destinée aux desktops comporte 8 P-Cores et 8 E-Cores. Du côté des modèles pour ordinateurs portables, une version comporte 6 P-Cores contre 8 E-Cores et l’autre, destinée aux ultra-mobiles, se réduit à 2 P-Cores pour 8 E-Cores.

Les puces d’Intel rassemble des blocs logiques, qualifiés par Arik Gihon, architecte en chef d’Alder Lake, de « blocs de construction » réunis de diverses façons. Sur le schéma ci-dessus, on voit que la puce pour desktop n’a pas les capacités Thunderbolt et a un plus petit nombre de coeurs graphiques intégrés que les puces pour ordinateurs portables. (Crédit : Intel) Agrandir l'image.

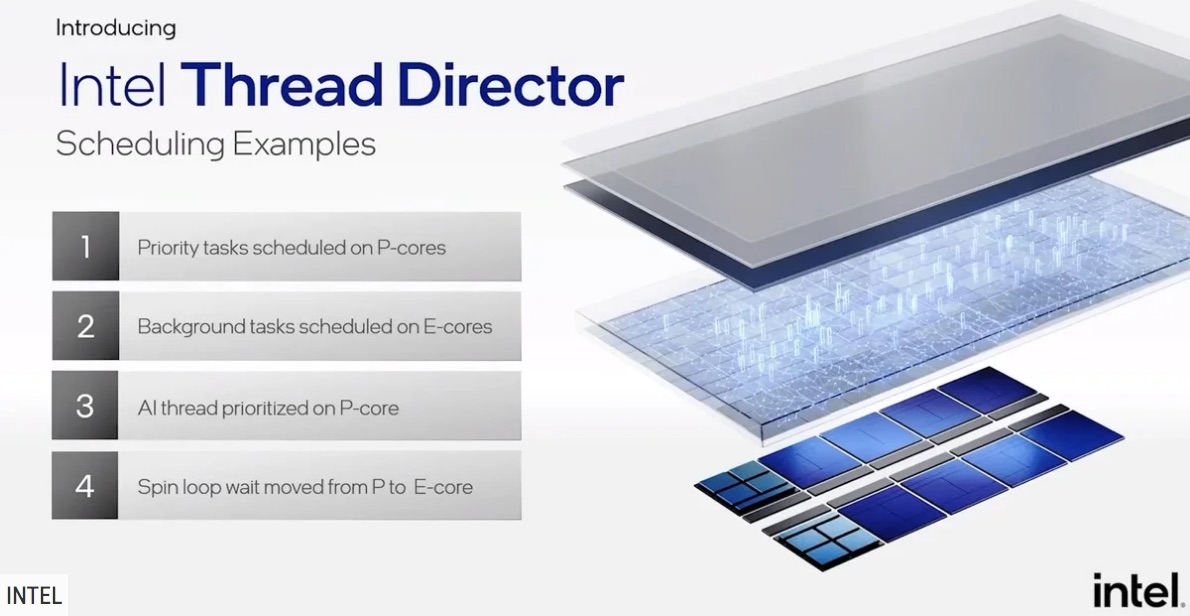

Le Thread Director est un planificateur de tâches qui garantit que les opérations de haute priorité sont traitées en premier et qu'un coeur ne manque pas de données. Jusqu'à présent, les applications exécutées au premier plan se voyaient attribuées la priorité la plus élevée. Thread Director va plus loin en analysant les besoins de performances de chaque thread et en les affectant au bon type de coeur puis en les réaffectant à la volée si d'autres threads se présentent. Comme il s'exécute dans le matériel et non dans le logiciel, les développeurs n'auront pas à essayer d'attribuer ces priorités eux-mêmes, en particulier pour les jeux, le streaming et les applications de productivité.

Thread Director peut réaffecter dynamiquement les threads entre les coeurs de performance et d'efficacité. (Crédit : Intel)

Parmi les changements à attendre sur Alder Lake, le processeur pour desktop utilisera un socket LGA1700 qui remplace le standard LGA775 utilisé depuis des années dans le monde du jeu. Ceux qui montent eux-mêmes leur PC devront donc racheter carte mère et dissipateur. Alder Lake utilise aussi une interface mémoire physique hybride qui supporte quatre différents types de mémoire : DDR4-3200, LPDDR4x-4266, ainsi que les modules DDR5-4800 and LPDDR5x pour la technologie DDR5. Alder Lake pourra réduire ou augmenter la cadence d’horloge pour réduire la consommation en fonction d’une analyse en temps réel des tâches effectuées. Enfin, Alder Lake inclura pour la première fois le support de PCI Express 5, annoncé en 2019. PCIe Gen 5 supporte jusqu’à deux fois le débit de PCIe 4, ou 64 GBps sur 16 voies.

Micro-architectures graphiques Xe HPG et Xe HPC

L’événement Architecture Day 2021 a également couvert les prochaines micro-architectures graphiques Xe HPG et Xe HPC. La première, Xe HPG, est conçue pour les applications de jeu et de création. C’est sur elle que s’appuiera la famille de SoC Alchemist dont le premier produit arrivera au premier trimestre 2022 sous le nom de marque Intel Arc. Elle comprend un nouveau cœur Xe, axé sur le calcul, programmable et évolutif. Quant à la micro-architecture Xe HPC, elle est destinée au calcul haute performance, à l’accélération des applications d’intelligence artificielle et analytiques avancées avec Ponte Vecchio, « le SoC le plus complexe qu’Intel ait jamais construit », a commenté Raja Koduri en le citant comme un exemple remarquable de la stratégie IDM (integrated device manufacturing) 2.0 d’Intel. « Ponte Vecchio tire parti de plusieurs procédés avancés de semiconducteurs, de notre technologie révolutionnaire EMIB [Embedded multi-die interconnect bridge] et de notre packaging Foveros 3D ». Sur l’Architecture Day, Intel a montré que les performances Ponte Vecchio dépassaient 45 TFlops FP32, avec un débit supérieur à 5 TBps sur le fabric mémoire et supérieur à 2 TBps sur la connectivité. Ponte Vecchio pourra être mis en oeuvre, comme les autres architectures Xe, à partir des outils et bibliothèques réunis dans le package logiciel ouvert oneAPI.

Sur son Architecture Day, Intel a aussi présenté son IPU (infrastructure processing unit) Mount Evans, un circuit d’accélération réseau basé sur un Asic, et sa plateforme de référence FPGA Oak Springs Canyon. Ceux-ci ont vocation à permettre aux fournisseurs de services cloud de transférer des tâches d’infrastructure des CPU aux IPU afin de pouvoir réserver la totalité des CPU de leurs serveurs à leurs clients. L’événement s’est clos sur un message du CEO Pat Gelsinger qui a repris les rênes d’Intel en janvier dernier et a entrepris de restructurer le groupe californien. Celui-ci a notamment rappelé que le prochain rendez-vous fixé autour des technologies du fabricant de processeurs, Intel Innovation, se tiendrait le 27 octobre prochain.

Commentaire