Outre la mise en place d’un groupe de travail pour le développement conjoint de SOC pour l’IA, Ampere a annoncé une augmentation du nombre de cœurs de ses puces serveur AmpereOne (3 nm gravées chez TSMC) basées sur un design Arm. Renee James, CEO d'Ampere et ancienne dirigeante d’Intel, a déclaré que les besoins croissants en énergie des processeurs pour l’IA n’étaient tout simplement pas viables et qu'Ampere représentait une meilleure alternative en la matière. « La voie actuelle n'est pas tenable », a-t-elle affirmé dans un communiqué. « L’infrastructure des centres de données de demain doit offrir de meilleures modalités de traitement dans les environnements existants refroidis par air, et être durable sur le plan environnemental en s'adaptant à l'énergie disponible sur le réseau. C'est à cela que travaille Ampere ».

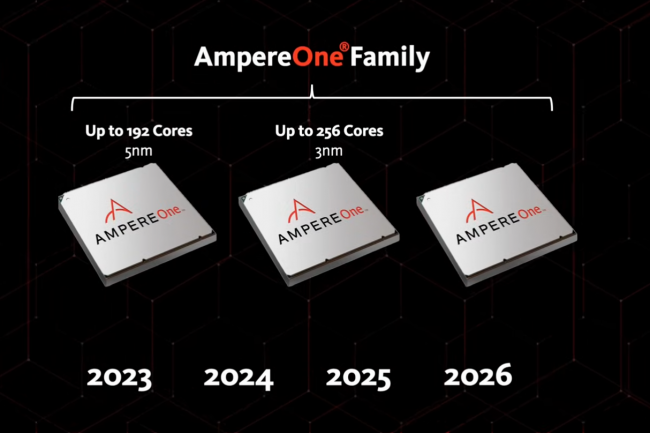

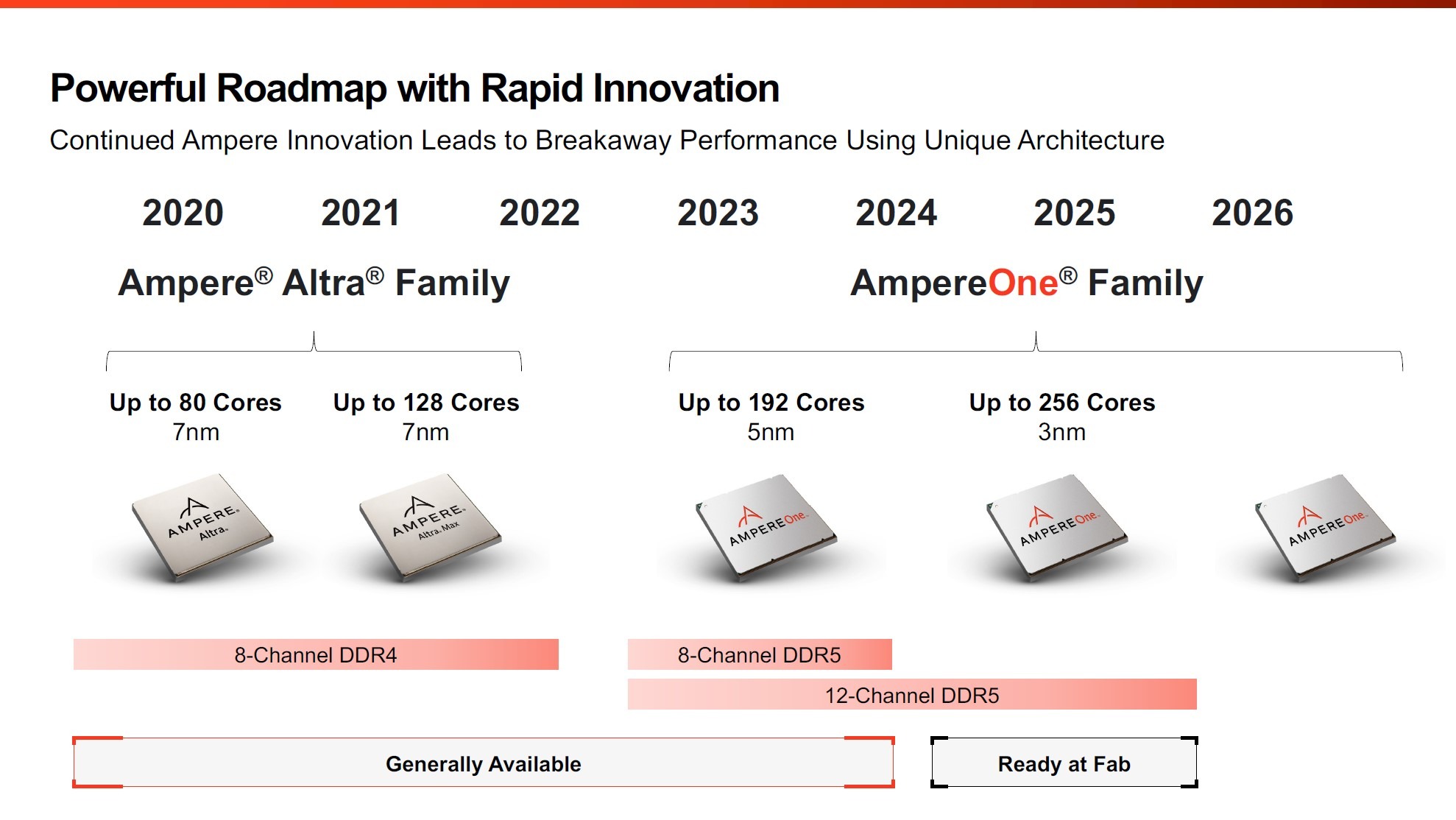

La feuille de route d'Ampere annonce des puces ARM pour serveur avec 256 coeurs. (Crédit Ampere)

En ce qui concerne les processeurs, la puce serveur haut de gamme AmpereOne passe de 192 à 256 cœurs et sa mémoire de 8 à 12 canaux, ce qui étend la bande passante. Jeff Wittich, chef de produit chez Ampere, a précisé qu’il était possible d’intégrer le processeur AmpereOne à 192 cœurs existant dans la plate-forme à 12 canaux, ce qui le rend compatible avec les évolutions futures. Malgré le nombre considérable de cœurs, le refroidissement liquide n'est pas nécessaire. « Aucun produit de notre feuille de route n'exige un refroidissement liquide. Nous facilitons donc le maintien de l'infrastructure actuelle des centres de données tout en offrant une efficacité énergétique meilleure que précédemment », a déclaré M. Wittich. Selon Ampere, dans les benchmarks de la norme industrielle Spec_Int, le processeur AmpereOne à 256 cœurs dépasse de 50 % les performances de l'AMD Genoa (96 cœurs) et de 15 % celles de l'AMD Bergamo (128 cœurs). M. Wittich a rappelé qu'Intel ne disposait pas d'un processeur comparable en nombre de cœurs. Un point important chez les hyperscalers pour la création d’instances.

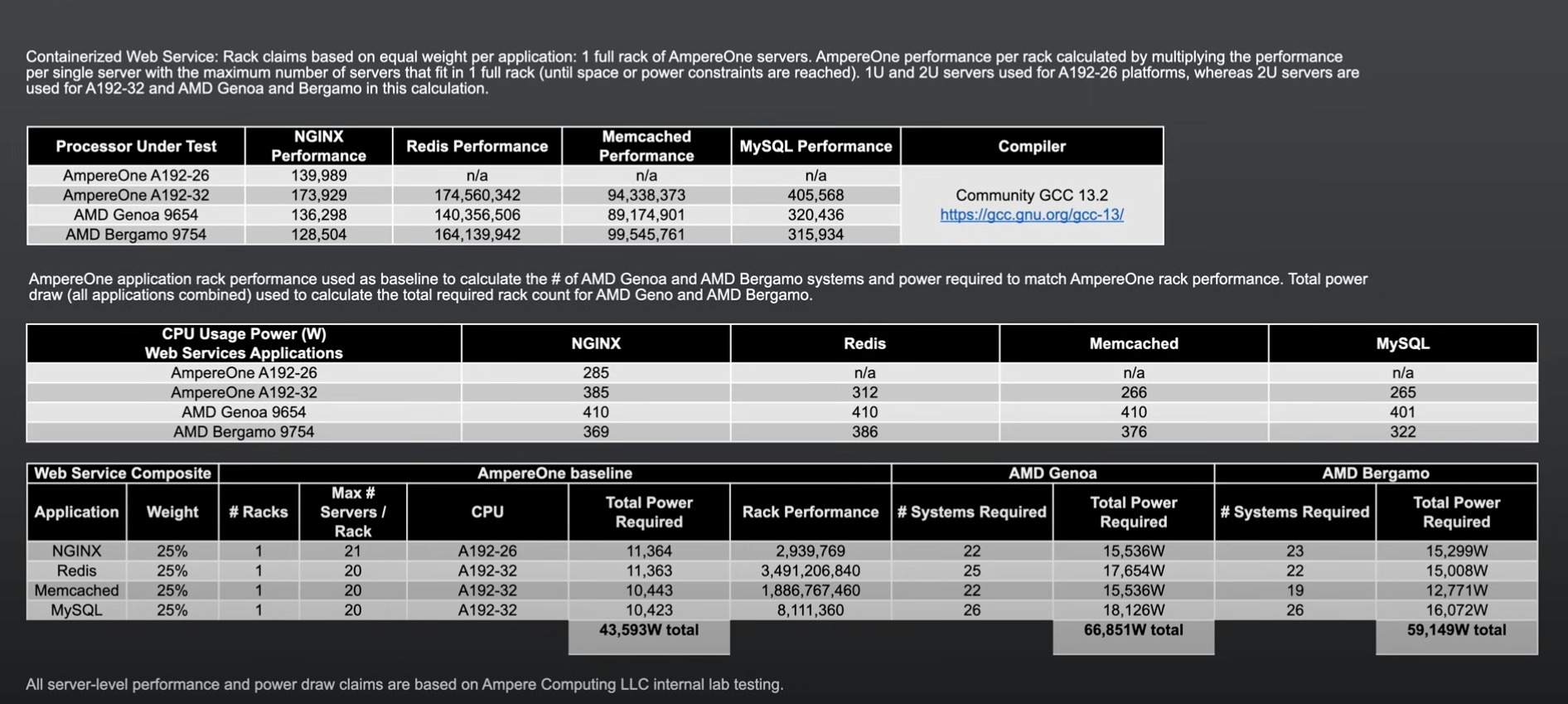

Face à AMD, Ampere présente des résultats flatteurs pour ses puces ARM multicoeurs. (Crédit Ampere)

Pour les opérateurs de centres de données qui cherchent à rafraîchir et à consolider l'ancienne infrastructure afin de récupérer de l'espace, du budget et de l'énergie, AmpereOne affirme que soin AmpereOne offre jusqu'à 34 % de performances supplémentaires par rack. « Nous sommes donc la solution la plus efficace en ce qui concerne le taux Spec_Int, et l’on peut évidemment traduire cela en performances au niveau du rack, des caractéristiques dont AMD et Intel commencent à parler davantage », a fait remarquer M. Wittich. Ce dernier reconnait que le benchmark n’équivaut pas à une charge de travail en situation réelle, mais selon lui, lorsqu'on le compare aux charges de travail typiques de la pile web comme Nginx, Redis, MySQL et Memcached, Ampere est en tête face à la concurrence. « Si l’on met tout cela ensemble et que l’on regarde ce qui se passe au niveau du rack, on a besoin de beaucoup moins d'espace, de beaucoup moins de serveurs et de 35 % de puissance en moins quand on déploie notre puce AmpereOne plutôt que des processeurs AMD Epyc Genoa ou Bergamo », a-t-il fait valoir.

De la performance avec une consommation électrique moindre

Par ailleurs, Ampere collabore avec Qualcomm Technologies pour développer une solution commune associant les processeurs Ampere et Cloud AI100 Ultra (Qualcomm). Cette solution s'attaquera à l'inférence LLM sur les plus grands modèles d'IA générative de l'industrie. Ampere a également annoncé que Meta's Llama 3 fonctionnait désormais sur ses puces dans Oracle Cloud. Les données de performance montrent que l'exécution de Llama 3 sur le CPU Ampere Altra à 128 cœurs (le prédécesseur d'AltraOne) sans GPU offre les mêmes performances qu'un GPU Nvidia A10 associé à un CPU x86, tout en utilisant un tiers de la puissance, selon Ampere. Enfin, l’entreprise a annoncé la formation d'un groupe de travail Universal Chiplet Interconnect express (UCIe) dans le cadre de l'AI Platform Alliance qu'elle a formée l'année dernière. Ce groupement de concepteurs de puces a pour ambition de mettre en commun les ressources et le talent pour faire progresser le développement des puces d'IA. L'UCIe est conçu autour de l'intégration ouverte de silicium, offrant une norme ouverte à l'ensemble de l'industrie pour construire des solutions au niveau du SOC où des puces de différentes entreprises sont intégrées dans un SOC. « L’industrie a besoin de solutions ouvertes qui soient largement disponibles pour tous, non exclusives et non propriétaires. C'est la raison pour laquelle nous construisons ces solutions de premier ordre au niveau du serveur, que l’on peut mettre rapidement sur le marché, et accessibles au plus grand nombre », a déclaré M. Wittich.

Commentaire