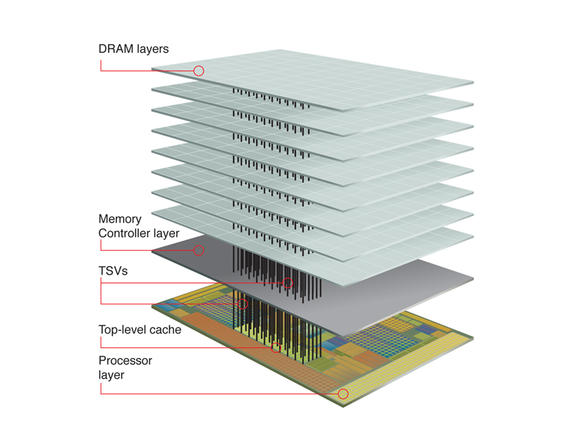

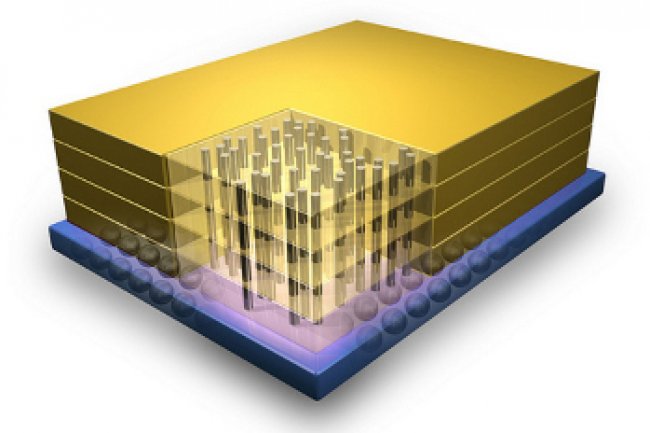

Un pas de plus a été franchi dans le développement de la Dram 3D. Le consortium Hybride Memory Cube (HMC), soutenu par une centaine d'entreprises dont Micron, Samsung et Hynix a finalisé les spécifications de la Dram 3D. Autrement appelé cube mémoire hybride, il prévoit d'empiler plusieurs mémoires volatiles sur un contrôleur de Dram. Cet empilement est connecté au contrôleur à travers la technologie VIA (Vertical Interconnect Access), un fil électrique placé verticalement reliant la puce et les mémoires.

Mike Black, chef technologique pour l'équipe de Micron au sein du consortium, explique que les développeurs ne vont changer que la structure de base de la Dram. « Nous avons pris les fonctionnalités de la Dram pour les faire dialoguer avec la couche logique de la puce à la base de cette pile 3D », explique le spécialiste. Il ajoute que « ce processus permet de tirer parti des transistors haute performance non seulement à travers la Dram, mais aussi de manière plus efficace avec le processeur hôte. Car la couche logique sert à la fois d'interconnexion avec ce processeur et le contrôleur de la Dram ».

Schéma de la composition de l'Hybrid Memory Cube

Dépasser les limitations de la DDR3 et 4

Selon les premières spécifications du consortium HMC, cette mémoire devrait se décliner en deux versions 2 et 4 Go, offrant une bande passante bidirectionnelle jusqu'à 160 Gbps. On est loin des 11 Gbps de la DDR3 ou des 18 à 20 Gbps de la DDR4, souligne Mike Black. Pour Jim Hnady, directeur du cabinet Objective Analysys, la technologie Hybrid Memory Cube résout certains problèmes importants. Aujourd'hui, les puces Dram sont limitées par les tracés des circuits intégrés et les connexions électriques en cuivre, alors que les besoins en traitement d'I/O progressent et demandent au bus des vitesses allant jusqu'à gigahertz, ce qui est très gourmand en énergie.

Selon l'analyste, la technologie HMC réduit les tâches que doit exécuter une Dram, avec une consommation électrique sur des distances plus courtes. « L'interface est 15 fois plus rapide que la Dram standard tout en réduisant la consommation électrique de 70%. Au fond, la beauté de la chose est qu'elle se débarrasse de toutes les questions qui empêchaient la DDR3 et la DDR4 d'aller aussi vite ».

Le consortium a dévoilé deux types d'interface physique pour la HMC se situant derrière un processeur hôte : une interconnexion courte portée et une à ultra-courte portée. La première ressemble à la plupart des technologies présentes sur les cartes mères, où la Dram est placée à 8 ou 10 pouces de la CPU. Cette technique s'adresse à une utilisation dans les applications réseaux et d'améliorer les débits en passant de 15 à 28 Gbps par broche. La seconde comprendra un Dram placée entre un et trois pouces de la CPU et s'adresse au réseau haute performance. Mike Black précise que l'interconnexion courte portée de la Hybrid Memory Cube est prévue au second semestre 2013 et l'ultra courte portée sera disponible l'année prochaine.

Les spécifications de la Dram 3D finalisées

0

Réaction

Les trois plus grands fabricants de mémoire ont annoncé les spécifications finales de la Dram 3D au sein du consortium Hybrid Memory Cube. Cette mémoire devrait améliorer les performances réseau et le calcul haute performance.

Newsletter LMI

Recevez notre newsletter comme plus de 50000 abonnés

Commentaire